# Capacitance extraction method of a free-standing bilayer lipid membrane formed over an aperture in a nanofabricated silicon chip

Yasutaka Tomioka<sup>1\*</sup>, Shogo Takashima<sup>1</sup>, Masataka Moriya<sup>1</sup>, Hiroshi Shimada<sup>1</sup>, Fumihiko Hirose<sup>2</sup>, Ayumi Hirano-Iwata<sup>3</sup> and Yoshinao Mizugaki<sup>1</sup>

<sup>1</sup>The University of Electro-Communications, Chofu, Tokyo, 182-8585, Japan. <sup>2</sup>Yamagata University, Yonezawa, Yamagata, 992-8510, Japan <sup>3</sup>Tohoku University, Aoba, Sendai, 980-8577, Japan

\*E-mail: tomioka@w8-7f.ee.uec.ac.jp

A bilayer lipid membrane (BLM) is a main component of a cell membrane of living organisms, which can be formed artificially. Although a specific capacitance of a BLM is known to be in the range of  $0.4 - 1.0 \ \mu\text{F} \text{ cm}^{-2}$ , many previous works forming free-standing BLMs over an aperture in silicon chips reported larger values beyond this typical range, which suggests that the equivalent circuit models are not adequate. In this work, we modified the equivalent circuit model by adding a resistance element of silicon. To evaluate the validity of the modified model, we applied the model to the results of electrochemical impedance spectroscopy (EIS) for free-standing BLMs formed over an aperture in nanofabricated silicon chip. The derived specific capacitance values were  $0.57 \pm 0.08 \ \mu\text{F} \text{ cm}^{-2}$ , which was settled in the typical range.

# **1. Introduction**

The human body comprises of several cells. The main component of cell membranes is a double layer of phospholipids. Phospholipids bilayers can be formed artificially and are expected to be applied for not only pharmaceutical products as well as electronics components. Among many forming methods, a membrane formed over an aperture is referred to as a free-standing bilayer lipid membrane (BLM). BLMs were formed over an aperture in Teflon films in early days;<sup>1)</sup> now there are many reports about BLMs formed on various platforms such as a porous alumina,<sup>2,3)</sup> an indium tin oxide (ITO),<sup>4)</sup> and so on.<sup>5,6)</sup> Especially, a silicon chip has an advantage in utilization of micro-nano-fabrication technologies. As examples of experiments using micro- and nano-fabricated silicon chips,<sup>5,6)</sup> ion-current recordings of cell-free-synthesized hERG channels embedded in a BLM<sup>7,8)</sup> and photomodulation of electrical conductivity of a PCBM-doped BLMs<sup>9)</sup> have been reported.

BLM capacitances per unit area (specific capacitances) have been reported to be in the range of  $0.4 - 1.0 \ \mu\text{F} \ \text{cm}^{-2}$  in many previous works.<sup>1-4,10-16)</sup> To determine the specific capacitance of a BLM, time-domain measurements<sup>1,6,16,17)</sup> (triangle waveform sweep, transient response) and frequency-domain measurement<sup>3-5,10-13,15,18-24)</sup> (electrochemical impedance spectroscopy: EIS) are often conducted. No matter what kind of measurement method is used, however, to determine the specific capacitance, experimental results are analyzed using the equivalent circuit of the system. Historically, specific capacitances of BLMs formed over an aperture in Teflon films were determined within the typical range (0.4 – 1.0  $\mu$ F cm<sup>-2</sup>)<sup>1</sup>, whereas those in silicon chips were often reported to be larger values than 1.0  $\mu$ F cm<sup>-2</sup>.<sup>17-22</sup> Since experiments were successful for both Telfon and silicon platforms, fault derivation for silicon chips were supposed to originate from equivalent circuits.

In this work, in order to determine the specific capacitances of BLMs formed over an aperture in nanofabricated silicon chips, we modified the equivalent circuit model, and conducted series experiments. We determined the parameters of the modified equivalent circuit, in which both capacitance and resistance of the silicon chip were included, by analyzing EIS results. In addition, we measured triangle waveform responses and compared them with circuit simulation of the equivalent circuit. Below we describe the validity of the modified circuit model both in the frequency- and time-domain. Determination of the BLM capacitance and resistance is also presented.

# **2.** Experimental methods

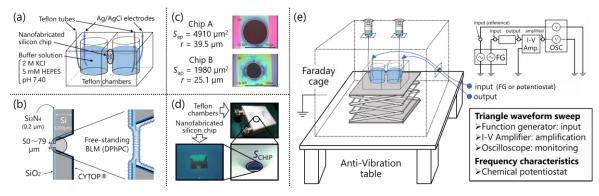

Figure 1 shows our experimental setup with detailed illustrations and photomicrographs. A

nanofabricated silicon chip was placed between two Teflon chambers as shown in Fig 1(a). Figure 1(b) shows detailed design of the silicon nanofabricated chip and a free-standing BLM. The fabrication process of an aperture in silicon chips was described in Refs. 7, 8, and 25. Figure 1(c) shows optical photomicrographs of apertures in two silicon chips. The aperture areas ( $S_{ap}$ ) of Chips A and B are 4910 and 1980 µm<sup>2</sup>, respectively. Figure 1(d) shows stereo microscope images of the Teflon chambers and the nanofabricated silicon chip sandwiched in between. The area of the silicon chip ( $S_{CHIP}$ ) contacting with buffer solution is 3.14 mm<sup>2</sup>. Teflon chambers with a nanofabricated silicon chip were placed in a Faraday cage on an anti-vibration table as shown in Fig. 1(e).

1,2-diphytanoyl-sn-glycero-3-phosphocholine (DPhPC) bilayer was formed by using Montal-Mueller's method<sup>1)</sup>. Firstly, the buffer solution of 2 M KCl mixed with 5 mM HEPES was poured in both wells (1400  $\mu$ l). Then, the buffer solution levels were lowered by operating syringes via Teflon tubes. Next, 5 mg ml<sup>-1</sup> solution of DPhPC (the solvent: chloroform / *n*-hexane, 1:1) was dropped in both wells. After the evaporation of the solvent, the buffer solution levels were raised slowly; a free-standing BLM was finally formed over an aperture in the nanofabricated silicon chip. Electrical measurements were conducted via silver-silver chloride electrodes. EIS was conducted with a chemical potentiostat (Bio-Logic, SP-200) in the frequency range from 3 MHz to 1 mHz with the input voltage of 70.7 mV<sub>peak</sub>. Triangle waveform response was measured with a function generator (Tektronix, AFG3252), a low noise current preamplifier (Stanford Research Systems, SR570), and an oscilloscope (Rohde & Schwarz, RTB2004). The amplitude and frequency of the triangle waveform were respectively set at 100 mV<sub>p-p</sub> (high level: 50 mV, low level: –50 mV) and 5 kHz.

EIS results were analyzed by using an equivalent circuit modeling software (ZView<sup>®</sup>, Scribner Associates), by which circuit parameters were determined. Then, triangle waveform response was simulated with the derived parameters by using an electronic circuit simulator (LTspice<sup>®</sup>, Linear Technology) and compared with the experimental results of triangle waveform responses.

# **3.** Capacitance extraction method

#### 3.1 Triangle waveform simulation

Under certain restrictions, a BLM capacitance can be extracted by using triangle waveform sweep<sup>6,16)</sup>. This method is based on the theory that constant current  $I_{out}$  is observed for the slope of a triangle waveform voltage applied to a capacitor. That is,  $I_{out}$  is expressed as

$$I_{\text{out}} = \frac{\mathrm{d}q}{\mathrm{d}t} = \frac{\mathrm{d}(C_{\text{triangle}}V_{\text{in}})}{\mathrm{d}t} = C_{\text{triangle}}\frac{\mathrm{d}V_{\text{in}}}{\mathrm{d}t} = 2V_{\mathrm{p-p}}f_{\mathrm{in}}C_{\mathrm{triangle}}.$$

(1)

Here, q is the charge on the capacitor,  $C_{\text{triangle}}$  is the capacitance,  $V_{\text{in}}$  is the applied input voltage.  $dV_{\text{in}}/dt$  of the gradient of a triangle can be transformed as  $2V_{\text{p-p}}f_{\text{in}}$ , where  $V_{\text{p-p}}$  is the amplitude, and  $f_{\text{in}}$  is the frequency ( $V_{\text{p-p}} = 100 \text{ mV}$ ,  $f_{\text{in}} = 5 \text{ kHz}$ ). The capacitance  $C_{\text{triangle}}$  can be calculated from the constant current  $I_{\text{out}}$  and the known values of  $V_{\text{p-p}}$  and  $f_{\text{in}}$ . This method is quite effective in case of BLMs formed on insulative platforms such as a Teflon film,<sup>1)</sup> a porous alumina,<sup>2-3)</sup> and other insulative ones<sup>6,16)</sup> for which a BLM can be simplified to a resistor-capacitor parallel model; when a BLM resistance is sufficiently high, the circuit model can be further simplified as a single capacitor.

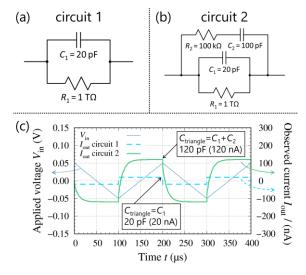

Figure 2(a) shows a resistor-capacitor parallel model (Circuit 1,  $C_1 = 20$  pF and  $R_1 = 1$  T $\Omega$ ). A triangle waveform simulation result for Circuit 1 is presented in Fig. 2(c) as a dashed curve. In simulation, ( $dV_{in}/dt$ ) at the slope was set at ±1000 V/s (0.1V/100µs). The constant value of  $I_{out}$  was ± 20 nA, by substituting these values into Eq. (1),  $C_{triangle}$  becomes 20 pF, which agreed with the configured value of  $C_1$  of 20 pF. Contrary, if a platform is not insulative, a circuit model becomes more complicated with the capacitance  $C_2$  and resistance  $R_2$  of the platform, which is shown in Fig. 2(b) (Circuit 2,  $C_1 = 20$  pF,  $R_1 = 1$  T $\Omega$ ,  $C_2 = 100$  pF, and  $R_2 = 100$  k $\Omega$ ). Figure 2(c) presents a triangle waveform simulation result for Circuit 2 as a thick solid curve. As can be seen, the observed current is distorted, whereas the constant current value is increased to 120 nA; the calculated capacitance  $C_{triangle}$  using Eq. (1) becomes the sum of two parallel capacitances ( $C_{triangle} = C_1 + C_2 = 120$  pF). As the circuit model becomes more detailed, the triangle waveform method with Eq. (1) cannot be used. Therefore, to divide the parallel capacitance, another method is required.

## 3.2 EIS and equivalent circuit analysis

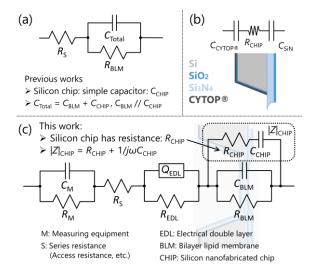

In this work, we took advantage of EIS and equivalent circuit analysis employed in many previous works.<sup>3-5,10-13,15,18-24</sup> Figure 3(a) shows an equivalent circuit for a BLM and a silicon chip having been used.<sup>18-24</sup> It is found that no resistance element of a silicon chip is included. Actually, although our previously proposed model succeeded to reproduce experimental model precisely, it was impossible to extract BLM capacitance because it did not take characteristics of a silicon chip into consideration.<sup>26</sup> Figure 3(b) shows a schematic illustration of a nanofabricated silicon chip with our modified equivalent circuit including the resistance of the silicon chip. As shown in Fig 1(b), the silicon body is covered by a Si<sub>3</sub>N<sub>4</sub> layer and a CYTOP<sup>®</sup> layer. (The insulative CYTOP<sup>®</sup> layer is employed to reduce current

noise.<sup>27)</sup> The model shown in Fig. 3(b) is then finally employed in the whole circuit model between two Ag/AgCl electrodes as shown in Fig. 3(c). The parallel  $R_{BLM}$  and  $C_{BLM}$  correspond to the BLM resistance and capacitance respectively. The series  $R_{CHIP}$  and  $C_{CHIP}$  correspond to the silicon chip's resistance and capacitance respectively [Fig 3(b)]. The parallel  $R_{EDL}$  and  $Q_{EDL}$  are electrical double layer (EDL) parameters; the  $Q_{EDL}$  is known as a constant phase element (CPE).<sup>5,11,19,20,28-30)</sup> The CPE reproduces the impedance of an EDL, which is written as

$$Z_{\rm CPE} = \frac{1}{(j\omega)^{\alpha} Q_{\rm EDL}}.$$

(2)

Here,  $\alpha$  is a constant value which moves in the range from 1 to 0. When  $\alpha = 1$ , it behaves as a capacitor, while  $\alpha = 0$ , it behaves as a resistor. The parameter of  $Q_{EDL}$  has a complex unit of F s<sup> $\alpha$ -1</sup>, where F is Farad, and s is second. The effective capacitance  $C_{EDL}$  can be calculated with the EDL parameters of  $R_{EDL}$  and  $\alpha$ , which is written as

$$C_{\rm EDL} = Q_{\rm EDL}^{1/\alpha} R_{\rm EDL}^{(1-\alpha)/\alpha}.$$

(3)

The parallel  $R_{\rm M}$  and  $C_{\rm M}$  correspond to the parasitic parameters of our experimental setup. The  $R_{\rm S}$  corresponds to the series resistance, most of which is occupied by an access resistance<sup>31,32)</sup> around the aperture in the nanofabricated silicon chip. The access resistance is expressed as

$$R_{\rm ac} = \frac{1}{2\kappa r}.$$

(4)

Here,  $\kappa$  is the conductivity of the buffer solution ( $\kappa = 0.23$  S cm<sup>-1</sup>, 2 M KCl), and *r* is the radius of the aperture [Fig. 1(c)].

#### 4. Results and discussion

#### 4.1 Equivalent circuit fitting and evaluation

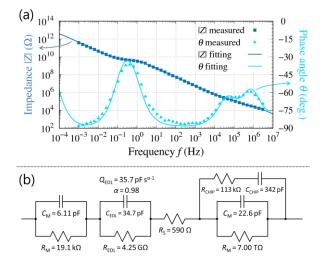

Figure 4(a) shows examples of EIS using Chip A and fitting results, in which the modulus and phase angle of impedance are plotted as functions of frequency, whereas Fig. 4 (b) shows an equivalent circuit model with the parameters obtained by fitting. The fitting curves agree well with the experimental results.

We conducted seven experiments in total (Chip A, n = 7). Membrane resistances  $R_{BLM}$  were extracted within a wide range from 12.2 G $\Omega$  to 7.00 T $\Omega$ , which are sufficiently high values to observe channel recordings. The maximum resistance of 7.00 T $\Omega$  (and its normalized value of  $R_{BLM} S_{ap} = 344 \text{ M}\Omega \text{ cm}^2$ ) obtained in the series experiments is higher than the values reported in previous works.<sup>1,3-5,10-13,18-24,33,34</sup>) Such a high membrane resistance indicates that the micro- and nano-tapered apertures fabricated in silicon chips

enhance not only the mechanical stability but also the electrical resistance of BLMs. Notably, previous researches forming free-standing BLMs, membrane resistances over apertures in silicon chips reported BLM resistances as high as 4.7 G $\Omega$  (160 M $\Omega$  cm<sup>2</sup>, DPhPC),<sup>3)</sup> 157 G $\Omega$  (12.3 M $\Omega$  cm<sup>2</sup>, POPC),<sup>17)</sup> 74 G $\Omega$  (6.0  $\Omega$  cm<sup>2</sup>, DPPE / DPPS),<sup>19)</sup> 53.6 G $\Omega$  (0.96 M $\Omega$  cm<sup>2</sup>, DPhPC);<sup>20)</sup> membrane resistances appear to be dependent on not only lipid molecules but also platform's micro- and/or nano-structures.

Membrane capacitances  $C_{\text{BLM}}$  were obtained as 28 ± 4 pF. The specific capacitance calculated by  $C_{\text{BLM}} / S_{\text{ap}} (S_{\text{ap}} = 4910 \,\mu\text{m}^2 \text{ is the aperture area of the nanofabricated chip [Fig. 1(c)]) was <math>0.57 \pm 0.08 \,\mu\text{F cm}^{-2}$ . This value falls within the range of  $0.4 - 1.0 \,\mu\text{F cm}^{-2}$  that have been reported in previous works.<sup>1-4,10-16</sup>

The resistance of the silicon chip  $R_{\text{CHIP}}$  was extracted as  $92 \pm 15 \text{ k}\Omega$ . Then, the resistivity of the chip can be calculated as follows:

$$\rho \simeq \frac{S_{\rm CHIP}}{l} R_{\rm CHIP}.$$

(5)

Here,  $S_{\text{CHIP}}$  of 3.14 mm<sup>2</sup> is the area of the nanofabricated silicon chip [Fig. 1(d)], *l* is the thickness of the silicon layer [Fig. 1(b)]. By using the Eq. 5, the resistivity of the chip becomes  $1.4 \pm 0.2 \text{ k}\Omega$  m, which agrees with the resistivity of high purity silicon crystal. The capacitance of the silicon chip  $C_{\text{CHIP}}$  was extracted as  $0.96 \pm 0.74$  nF. The relatively large deviation in  $C_{\text{CHIP}}$  was likely to attribute to the deviation in the spectra in low frequency (< 1 Hz) regions, where relatively long time was necessary for measurements, and hence, external noise and time evolution of BLM characteristics could be included. In addition, the chip surface modified and covered with a silane coupling agent and CYTOP<sup>®</sup> layer [Fig. 1(b)] was gradually changed, resulting in variation of  $C_{\text{CHIP}}$ .

$R_{\rm S}$  was extracted as 1.0 ± 0.4 kΩ, which is slightly higher than the calculated access resistance of 0.42 kΩ (using Eq. (4),  $r = 39.5 \,\mu\text{m}$ ).  $R_{\rm M}$  and  $C_{\rm M}$  were extracted respectively as 16 ± 2 kΩ and 7 ± 1 pF. We considered that  $R_{\rm M}$  and  $C_{\rm M}$  come from the low-current detection unit in the chemical potentiostat and the stray capacitance. EDL capacitances  $C_{\rm EDL}$ were obtained as 50 ± 10 pF, which was calculated from extracted parameters of  $R_{\rm EDL}$ ,  $\alpha$ , and  $Q_{\rm EDL}$  ( $R_{\rm EDL}$ : 3.2 ± 0.6 GΩ,  $\alpha$ : 0.97 ± 0.01,  $Q_{\rm EDL}$ : 51 ± 11 pF s<sup> $\alpha$ -1</sup>) by using Eq. (5).

# 4.2 Triangle waveform analysis

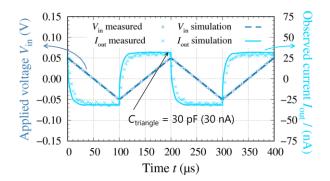

Besides frequency-domain characteristics discussed above, we also measured and analyzed time-domain characteristics by using triangle waveform sweep. We simulated a triangle waveform response by using the equivalent circuit with obtained parameters shown in Fig.

4(b). Figure 5 shows experimental and numerical results of triangle waveform response. Numerical results agree well with the experimental results, which supports that the EIS analysis with our modified equivalent circuit works effectively. From the gradient of the triangle  $(dV_{in}/dt = 100 \text{ mV}_{p-p} / 100 \text{ }\mu\text{s} = 10^3 \text{ V s}^{-1})$  and the observed constant current (30 nA),  $C_{\text{triangle}}$  was calculated by Eq. (1) as 30 pF. This value is larger than  $C_{\text{BLM}}$  of 22.6 pF shown in Fig. 4(b), which shows the traditional method overestimates the  $C_{\text{BLM}}$  value for BLMs formed over an aperture in silicon chips, as described in the Sect. 3.1.

# 4.3 Reproducibility of the capacitance extraction method

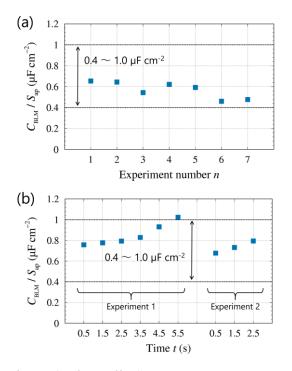

In order to confirm reproducibility of the capacitance extraction method, successive experiments were conducted. In these experiments, two silicon chips with different aperture dimensions shown in Fig. 1(c) were used. Figures 6(a) and 6(b) show the specific capacitances calculated from the extracted membrane capacitances of BLMs on Chips A and B, respectively. In the experiment using Chip A, seven experiments were conducted; EIS was conducted once in each experiment on a different day. In the experiment using Chip B, EIS was conducted every 1 hour to observe the time evolution of the specific capacitances (*t* of 0 represents the time of the BLM formation in Fig. 6(b)). As a result, the all specific capacitances fell into the range of  $0.4 - 1.0 \ \mu F \ cm^{-2}$  (at most  $1.02 \ \mu F \ cm^{-2}$ , t = 5.5 hours in Fig. 6(b)). In addition, it should be noted that continuous increases in the specific capacitances were observed, which were often reported in previous works.<sup>11,13,19,24,34</sup>

# **5.** Conclusion

We formed the free-standing BLMs over an aperture in nanofabricated silicon chips. We measured frequency characteristics to evaluate the electrical characteristics of the free-standing BLMs. The specific capacitances of BLMs were calculated using the experimental frequency characteristics and our modified equivalent circuit model including the silicon chip resistance in series with its capacitance. The membrane resistances were successfully extracted, up to 7.00 T $\Omega$  (334 M $\Omega$  cm<sup>2</sup>). This value is higher than the reported values in previous works. The specific capacitances were obtained as  $0.57 \pm 0.08 \ \mu\text{F cm}^{-2}$ , which fell into the range of  $0.4 - 1.0 \ \mu\text{F cm}^{-2}$ . We also confirmed that specific capacitances were obtained within the range of  $0.4 - 1.0 \ \mu\text{F cm}^{-2}$  throughout successive experiments. We also measured the triangle waveform responses to compare them with the numerical responses of the modified equivalent circuit model. The numerical results reproduced the experimental

results. These results demonstrated that the capacitance extraction method using EIS measurements and the modified equivalent circuit worked effectively for the free-standing BLMs formed over an aperture in silicon chips.

# Acknowledgments

This work was partly supported by JST-CREST Grant Number JPMJCR14F, and by JSPS KAKENHI Grant Number 17K04979. Nation-wide Cooperative Research Projects, Research Institute of Electrical Communication, Tohoku University are also acknowledged.

# References

- 1) M. Montal and P. Mueller, PNAS 69, 3561 (1972).

- A. Hirano-Iwata, T. Taira, A. Oshima, Y. Kimura and M. Niwano, Appl. Phys. Lett. 96, 213706 (2010).

- 3) W. Römer and C. Steinem, Biophys. J. 86, 955 (2004).

- 4) X. Wang, Y. Zhang, H. Bi and X. Han, RSC Adv. 6, 72821 (2016).

- 5) S. Rameshkumar and M. Kumaravel, Electrochim. Acta 245, 489 (2017).

- Z. Aminipour, M. Khorshid, M. Bayoumi, P. Losada-Pérez, R. Thoelen, S. Bonakdar, H. Keshvari, G. Maglia, P. Wagner and B. Van der Bruggen, Phys. Status Solidi A 214, 1700104 (2017).

- D. Tadaki, D. Yamaura, S. Araki, M. Yoshida, K. Arata, T. Ohori, K. Ishibashi, M. Kato, T. Ma, R. Miyata, Y. Tozawa, H. Yamamoto, M. Niwano and A. Hirano-Iwata, Sci. Rep. 7, 17736 (2017).

- D. Tadaki, D. Yamaura, K. Arata, T. Ohori, T. Ma, H. Yamamoto, M. Niwano and A. Hirano-Iwata, Jpn. J. Appl. Phys. 57, 03EA01 (2018).

- K. Kanomata T. Deguchi, T. Ma, T. Haseyama, M. Miura, D. Yamaura, D. Tadaki, M. Niwan, A Hirano-Iwata and F. Hirase, J. Electroanal. Chem. 832, 55 (2019).

- 10) K. Sugihara, J Vörös and T. Zambelli, ACS Nano 4, 5047 (2010).

- M. S. Khan, N S. Dosoky, G. Mustafa, D. Patel, B. Berdiev and D. Williams, Langmuir 33, 13680 (2017).

- V. Nikolov, J. Lin, M. Merzlyakov, K. Hristova and P. C. Searson, Langmuir 23, 13040 (2007).

- X. Wang, S. Ma, Y. Su, Y. Zhang, H. Bi, L. Zhang and X. Han, Anal. Chem. 87, 2094 (2015).

- 14) S. Kalsi, A. M. Powl, B. A. Wallace, H. Morgan and M. R. R. de Planque, Biophys. J.

106, 1650 (2014).

- C. G. Cranfield, S. T. Henriques, B. Martinac, P. Duckworth, D. J. Craik and B. Cornell, Langmuir 33, 6630 (2017).

- R. P. Carney, Y. Astier, T. M. Carney, K. Voitchovsky, P. H. J. Silva and F. Stellacci, ACS Nano 7, 932 (2013).

- 17) M. Eray, N. S. Dogan and L. Liu, Biosens. Bioelectron. 9, 343 (1994).

- X. Han, A. Studer, H. Sehr, I. Geissbühler, M. D. Berardino, F. K. Winkler and L. X. Tiefenauer, Adv. Mater. 19, 4466 (2007).

- 19) M. S. Khan, N. S. Dosoky, B. K. Berdiev and J. D. Williams, Eur. Biophys. J. 45, 843

(2016).

- Z.-W. Zhu, Y. Wang, X. Zhang, C.-F. Sun, M.-G. Li, J.-W. Yan and B.-W. Mao, Langmuir 28, 14739 (2012).

- C. E. Korman, M. Megens, C. M. Ajo-Franklin and D. A. Horsley, Langmuir 29, 4421 (2013).

- M. Ł. Górzny, N. L. Opara, V. A. Guzenko, V. J. Cadarso, H. Schift, X. D. Li and C. Padeste, Micro and Nano Engineering 3, 32 (2019).

- 23) T. Kaufeld, C. Steinem and C. F. Schmidt, J. Phys. D 48, 025401 (2015).

- 24) D. Weiskopf, E. K. Schmitt, M. H. Klühr, S. K. Dertinger and C. Steinem, Langmuir 23, 9134 (2007).

- D. Yamaura, D. Tadaki, S. Araki, M. Yoshida, K. Arata, T. Ohori, K. Ishibashi, M. Kato, T. Ma, R. Miyata, H. Yamamoto, R. Tero, M. Sakuraba, T. Ogino, M. Niwano and A. Hirano-Iwata, Langmuir 34, 5615 (2018).

- 26) Y. Tomioka, S. Takashima, M. Moriya, H. Shimada, F. Hirose, A. Hirano-Iwata and Y. Mizugaki, Jpn. J. Appl. Phys. 58, SDDK02, (2019).

- A. Oshima, A. Hirano-Iwata, T. Nasu, Y. Kimura and M. Niwano, Micro and Nanosystems 4, 2 (2012).

- 28) G. J. Brug, A. L. G. van den Eeden, M. Sluyters-Rehbach, J. H. Sluyters, J. Electroanal. Chem. 176, 275 (1974).

- 29) B. Hirschorn, M. E. Orazem, B. Tribollet, V. Vivier, I. Frateur and M. Musiani, Electrochim. Acta **55**, 6218 (2010).

- B. Hirschorn, M. E. Orazem, B. Tribollet, V. Vivier, I. Frateur and M. Musiani, J. Electrochem. Soc. 157, C452 (2010).

- 31) J. E. Hall, J. Gen. Physiol. 66, 531 (1975).

- 32) I. Vodyanoy and S. M. Bezrukov, Biophys. J. 62, 10 (1992).

- M. S. Khan, N. S. Dosoky, D. Patel, J. Weimer and J. D. Williams, Biosensors 7, 26 (2017).

- A. Beerlink, P.-J. Wilbrandt, E. Ziegler, D. Carbone, T. H. Metzger and T. Salditt, Langmuir 24, 4952 (2008).

# **Figure Captions**

**Fig. 1.** (Color online) (a) Schematic illustration of Teflon chambers with a sandwiched nanofabricated silicon chip. (b) Detailed illustrations of the cross-sectional view of the nanofabricated silicon chip and a free-standing bilayer lipid membrane (BLM) formed over an aperture in the chip. (c) Optical photomicrographs of apertures in two silicon chips (Chips A and B). (d) Stereo microscope images of the Teflon chambers and the nanofabricated silicon chip sandwiched in between. (e) Schematic illustration of the overall experimental setup with the block diagram of measuring equipment used for triangle waveform sweep.

**Fig. 2.** (Color online) (a) Traditional *RC* parallel circuit (Circuit 1) of a BLM. Electric elements of the platform are ignored. (b) Circuit model (Circuit 2) including  $R_2$  and  $C_2$  of the semiconducting platform. (c) Simulation results of triangle waveform sweep. Observed current  $I_{out}$  of Circuit 1 (dashed line), and Circuit 2 (solid line) are shown. The amplitude and the frequency of the input triangle potential  $V_{in}$  are 100 mV<sub>p-p</sub> at 5 kHz.

**Fig. 3.** (Color online) (a) Equivalent circuit model used in previous works. Total capacitance  $C_{\text{Total}}$  is the sum of the membrane capacitance  $C_{\text{BLM}}$  and the chip capacitance  $C_{\text{CHIP}}$ . (b) Schematic illustration of a silicon chip and its detailed equivalent circuit. (c) Whole circuit model between two Ag/AgCl electrodes.

**Fig. 4.** (Color online) (a) Examples of EIS results plotted with fitting curves. (b) Equivalent circuit model with the extracted parameters. The fitting was performed using ZView<sup>®</sup>.

**Fig. 5.** (Color online) Experimental and numerical results of triangle waveform response. Numerical simulation was executed by using the equivalent circuit model and parameters presented in Fig. 4(b). Fig. 6. (Color online) Specific capacitances obtained from the EIS experiment and fitting method using the modified equivalent circuit. (a) Results for Chip A. (b) Results for Chip B. All values were settled within the range of  $0.4 - 1.0 \ \mu\text{F} \text{ cm}^{-2}$  except for one result at t = 5.5 h in Chip B.

Fig. 1. (Color online)

Fig. 2. (Color online)

Fig. 3. (Color online)

Fig. 4. (Color online)

Fig. 5. (Color online)

Fig. 6. (Color online)