# Design and Evaluation of an FPGA-based Query Accelerator for Data Streams

by Yasin Oge

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

> Graduate School of Information Systems The University of Electro-Communications Tokyo, Japan

> > March 2016

# Design and Evaluation of an FPGA-based Query Accelerator for Data Streams

by Yasin Oge

Supervisory Committee: Prof. Tsutomu Yoshinaga, Chair Prof. Hiroshi Nagaoka Prof. Hiroyoshi Morita Prof. Satoshi Kurihara Prof. Tadashi Ohmori Copyright © 2016 Yasin Oge All Rights Reserved

概要

近年、データストリームに対するリアルタイム処理の重要性が高まってきている.特にストリーム処理に特化したデータストリーム管理システム (Data Stream Management System, DSMS) は、 理論的に無限のデータストリームに対して SQL ライクな継続的クエリを実行することでリアルタ イム処理を実現する.このような背景の中で、増加し続けるデータ量に対してリアルタイムなレ スポンスを提供する手段として FPGA (field-programmable gate array) に代表されるプログラマブ ル・デバイスをクエリ処理専用のアクセラレータとして活用する取り組みが注目されている.本 論文は、データストリーム処理におけるウィンドウ集約クエリの高速化を目的として、FPGA を 用いたクエリ・アクセラレータの設計・評価に関する研究について記述したものである.

本論文では、まず関連研究の説明を通して本研究の立ち位置を明確化した後、3つの研究課題 とそれぞれの解決方法を示している.1つ目の研究課題として、従来研究のデータストリーム処理 専用ハードウェアでは入力データ(タプル)の順序の乱れへの対応が考慮されていなかった問題 が挙げられる.そこで本研究は、順序の乱れた入力タプルを許容する効率的なハードウェア実装 |方法を提案している.2 つ目の研究課題は,オーバラップするスライディング・ウィンドウの増加 に対して性能及び面積の観点からスケールしない問題を解決するハードウェア設計方法を示すこ とである. そこで, オーバラップするスライディング・ウィンドウをペイン (pane) と呼ばれる サブ・ウィンドウに分割し、アグリゲーション(集約)処理を2段階に分けてパイプライン実装 する. この際 FPGA 内部のメモリ・ブロック(Block RAM, BRAM)を有効活用することで、従来 手法と比較して、性能と面積の両観点において優れたスケーラビリティを実現する.3つ目の研究 課題は、クエリ処理内容の変更に伴うオーバーヘッドによりクエリの実行時(ランタイム時)の コンフィギュレーションが困難な点の解決である.本研究では、この問題を解決する動的再構成 可能なクエリ・アクセラレータ「Configurable Query Processing Hardware (CQPH)」のアーキテク チャを提案している.提案アーキテクチャの実現可能性と有効性を示すことを目的として、Xilinx の FPGA 開発ボードを用いて CQPH のプロトタイプを実装・評価した.実機を用いた実験の結果, ギガビット・イーサネットの実効速度で受信したパケットを取りこぼすことなく連続して処理でき ることを確認した.また、より高速な入力インターフェイスとして DRAM を用いた実機テストで は、10Gbps 以上の入力ストリームに対して、複数のクエリを並列処理できることを示している.

# Abstract

An important and growing class of applications requires to process online data streams on the fly in order to identify emerging trends in a timely manner. Data Stream Management Systems (DSMSs) deal with potentially infinite streams of data that should be processed for real-time applications, executing SQL-like continuous queries over data streams. In order to deliver real-time response for high-volume applications, there is currently a great deal of interest in the potential of using field-programmable gate arrays (FPGAs) as custom accelerators for continuous query processing over data streams.

One of the previous studies focuses on sliding-window aggregate queries and shows how these queries can be implemented on an FPGA. Nevertheless, there still remain three practical issues related to the implementation of sliding-window aggregation. The first issue is that it is necessary to consider out-of-order arrival of tuples at a windowing operator. To address the issue, this work presents an orderagnostic implementation of a sliding-window aggregate query on an FPGA. The second issue is that a large number of overlapping sliding-windows cause severe scalability problems in terms of both performance and area. Instead of replicating a large number of aggregation modules, each sliding window is divided into non-overlapping sub-windows called panes. Results obtained in this work indicate that the pane-based approach can provide significant benefits in terms of performance (i.e., the maximum allowable clock frequency), area (i.e., the hardware resource usage), and scalability. Finally, the third issue is that there is a lack of run-time configurability, which severely limits the practical use in a wide range of applications. To address the problem, the present study proposes a novel query accelerator, namely Configurable Query Processing Hardware (CQPH). CQPH is an FPGA-based query processor that contains a collection of configurable hardware modules, especially designed for sliding-window aggregate queries. As a proof of concept, a prototype of CQPH is implemented on an FPGA platform for a case study. Evaluation results indicate that the prototype implementation of CQPH with a Gigabit Ethernet interface can process a packet stream at wire-speed without packet loss. Since the Gigabit Ethernet is not sufficient to saturate the CQPH, a DDR3 SDRAM module is used as a high-speed data source. Results indicate that the prototype of CQPH can execute multiple queries simultaneously without sacrificing the performance (i.e., throughput) even if the data rate reached more than 10 Gbps.

# Contents

| 1 | Intr  | oduction                                                    | 1      |

|---|-------|-------------------------------------------------------------|--------|

|   | 1.1   | Motivating Issues                                           | <br>1  |

|   |       | 1.1.1 Out-of-order arrival of tuples                        | <br>2  |

|   |       | 1.1.2 Scalability issue for overlapping sliding-windows     | <br>2  |

|   |       | 1.1.3 Lack of run-time configurability                      | <br>3  |

|   | 1.2   | Objectives                                                  | <br>3  |

|   |       | 1.2.1 Order-agnostic implementation technique               | <br>3  |

|   |       | 1.2.2 Efficient and scalable hardware design                | <br>4  |

|   |       | 1.2.3 CQPH: Configurable Query Processing Hardware          | <br>4  |

|   | 1.3   | Organization of the Dissertation                            | <br>4  |

| 2 | Bacl  | sground and Related Work                                    | 5      |

|   | 2.1   | Data Processing on FPGAs                                    | <br>5  |

|   |       | 2.1.1 Acceleration of Data-intensive Operations using FPGAs | <br>5  |

|   |       | 2.1.2 Continuous Query Processing on FPGAs                  | <br>5  |

|   |       | 2.1.3 Run-time Configuration of FPGAs                       | <br>7  |

|   | 2.2   | Sliding-Window Aggregation                                  | <br>7  |

|   |       | 2.2.1 Example of a sliding-window aggregate query           | <br>7  |

|   |       | 2.2.2 Handling out-of-order arrival of tuples               | <br>9  |

| 3 | Slidi | ng-window Aggregate Operator over Out-of-order Data Streams | 11     |

|   | 3.1   | Abstract                                                    | <br>11 |

|   | 3.2   | Design Concept                                              | <br>11 |

|   | 3.3   | Motivating Application                                      | <br>12 |

|   | 3.4   | Implementation Details                                      | <br>13 |

|   |       | 3.4.1 Wiring Interface                                      | <br>13 |

|   |       | 3.4.2 Hardware Execution Plan                               | <br>14 |

|   | 3.5  | Evaluation                                               | 20 |

|---|------|----------------------------------------------------------|----|

|   |      | 3.5.1 Resource Utilization and Performance               | 20 |

|   |      | 3.5.2 Experimental Measurement                           | 24 |

| 4 | Scal | able Implementation of Sliding-window Aggregate Operator | 26 |

|   | 4.1  | Abstract                                                 | 26 |

|   | 4.2  | Scalability Issue                                        | 26 |

|   |      | 4.2.1 Glacier                                            | 26 |

|   |      | 4.2.2 WID-based Implementation                           | 27 |

|   | 4.3  | Design Concept                                           | 28 |

|   |      | 4.3.1 Sliding Windows and Panes                          | 28 |

|   |      | 4.3.2 Two-Step Aggregation: PLQ and WLQ                  | 28 |

|   |      | 4.3.3 Hardware Cost Model                                | 31 |

|   | 4.4  | Implementation Details                                   | 33 |

|   |      | 4.4.1 Hardware Execution Plan                            | 33 |

|   |      | 4.4.2 Implementation of Pane-Level Sub-Query (PLQ)       | 35 |

|   |      | 4.4.3 Implementation of Window-Level Sub-Query (WLQ)     | 38 |

|   | 4.5  | Evaluation                                               | 40 |

|   |      | 4.5.1 Resource Utilization and Performance               | 41 |

|   |      | 4.5.2 Experimental Measurement                           | 43 |

| 5 | Con  | figurable Query Processing Hardware for Data Streams     | 45 |

|   | 5.1  | Abstract                                                 | 45 |

|   | 5.2  | Hardware Design Issue                                    | 45 |

|   | 5.3  | Design Concept                                           | 46 |

|   |      | 5.3.1 On-the-fly Query Configuration                     | 46 |

|   |      | 5.3.2 Supported Capabilities of CQPH                     | 49 |

|   | 5.4  | CQPH Architecture                                        | 51 |

|   |      | 5.4.1 Overview of CQPH                                   | 51 |

|   |      | 5.4.2 Selection Operator                                 | 54 |

|   |      | 5.4.3 Group-by Operator                                  | 56 |

|   |      | 5.4.4 Window-aggregation Operator                        | 59 |

|   |      | 5.4.5 Union Operator                                     | 61 |

|   | 5.5  | Evaluation                                               | 63 |

|   |      | 5.5.1 Latency and Throughput                             | 63 |

|   |      |                                                          |    |

|     |        | 5.5.2    | Dynamic Configuration Time       | 64 |

|-----|--------|----------|----------------------------------|----|

|     |        | 5.5.3    | Case Study                       | 65 |

| 6   | Con    | clustion | S                                | 74 |

|     | 6.1    | Summa    | шу                               | 74 |

|     | 6.2    | Future   | Work                             | 75 |

| Ac  | know   | ledgem   | ent                              | 77 |

| Re  | feren  | ces      |                                  | 78 |

| Lis | t of P | ublicati | ions Related to the Dissertation | 83 |

# **List of Figures**

| 2.2.1 $Q_1$ : "Find the maximum bid-price for the past 4 minutes and update the result every 1                                                             |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| minute."                                                                                                                                                   | 8  |

| 2.2.2 Overlapping Sliding-Windows for Query $Q_1$ (RANGE = 4 minutes and SLIDE = 1                                                                         |    |

| minute).                                                                                                                                                   | 9  |

| 3.3.1 The schema of the input stream. Each tuple of the stream consists of four attributes:                                                                |    |

| Symbol, Price, Volume, and Time                                                                                                                            | 13 |

| 3.3.2 $Q_2$ : "Count the number of trades of UBS (Union Bank of Switzerland) shares for the                                                                |    |

| past 10 minutes (600 seconds) and update the result every 1 minute (60 seconds)."                                                                          | 13 |

| 3.4.1 Wiring Interface for a query $q$                                                                                                                     | 14 |

| 3.4.2 Hardware execution plan for Query $Q_2$                                                                                                              | 15 |

| 3.4.3 Block diagram of a window-aggregation module                                                                                                         | 16 |

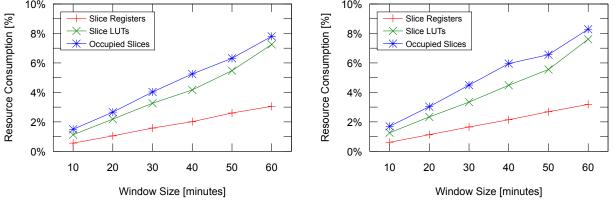

| 3.5.1 Overall resource consumption as a percentage of the total available resources on the                                                                 |    |

| target FPGA (Xilinx XC6VLX240T) with respect to the window size ( <i>i.e.</i> , RANGE)                                                                     | 21 |

| (a) Baseline implementation with $SLACK = 0. \dots $ | 21 |

| (b) Proposed implementation with $SLACK = 60.$                                                                                                             | 21 |

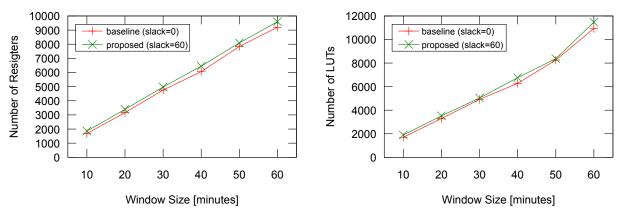

| 3.5.2 Comparison of the resource usage between the baseline implementation (SLACK = $0$ )                                                                  |    |

| and the proposed implementation ( $SLACK = 60$ )                                                                                                           | 22 |

| (a) Comparison of the number of registers                                                                                                                  | 22 |

| (b) Comparison of the number of LUTs                                                                                                                       | 22 |

| (c) Comparison of the number of slices                                                                                                                     | 22 |

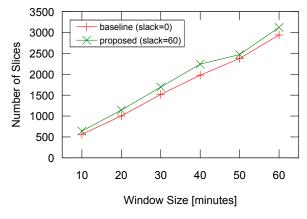

| 3.5.3 Maximum clock frequencies of the implemented design on the target FPGA (Xilinx                                                                       |    |

| XC6VLX240T) with respect to the window size ( <i>i.e.</i> , <i>RANGE</i> )                                                                                 | 23 |

| (a) Baseline implementation with $SLACK = 0. \dots $ | 23 |

| (b) Proposed implementation with $SLACK = 60.$                                                                                                             | 23 |

| 3.5.4 Overview of the Experimental System                                                                                                                  | 24 |

| 4.3.1 I | Relat  | ionship between overlapping sliding-windows and non-overlapping panes                                  | 29       |

|---------|--------|--------------------------------------------------------------------------------------------------------|----------|

| (       | (a)    | Overlapping Sliding-Windows for Query $Q_1$ cited from Chapter $2(RANGE = 4$                           |          |

|         |        | minutes and $SLIDE = 1$ minute)                                                                        | 29       |

| (       | (b)    | Each sliding window of Query $Q_1$ is divided into four non-overlapping sub-windows                    |          |

|         |        | ( <i>i.e.</i> , panes), each of which has $RANGE = 1$ minute and $SLIDE = 1$ minute, re-               |          |

|         |        | spectively                                                                                             | 29       |

| 4.3.2 9 | Q3: '  | Find the maximum <i>bid-price</i> as <i>p-max</i> for the past <i>1 minute</i> and update the result   |          |

| e       | every  | <i>1 minute</i> ."                                                                                     | 30       |

| 4.3.3 🤇 | Q4: '  | Find the maximum <i>p-max</i> value for the past <i>4 minutes</i> and update the result every          |          |

| 1       | 1 mir  | nute."                                                                                                 | 31       |

| 4.4.1 I | Hard   | ware execution plan for Query $Q_2$                                                                    | 34       |

| 4.4.2 I | Bloc   | k diagram of a PLQ aggregate module.                                                                   | 38       |

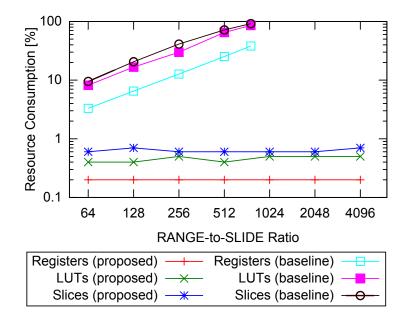

| 4.5.1 0 | Com    | parison of the overall resource consumption between the pane-based implementa-                         |          |

| t       | tion ( | (labeled "proposed") and the WID-based implementation presented in Chapter 3(la-                       |          |

| ł       | beled  | l "baseline")                                                                                          | 41       |

| 4.5.2 0 | Com    | parison of the maximum clock frequency between the pane-based implementation                           |          |

| (       | (labe  | led "proposed") and the WID-based implementation presented in Chapter 3(labeled                        |          |

| •       | "base  | eline")                                                                                                | 43       |

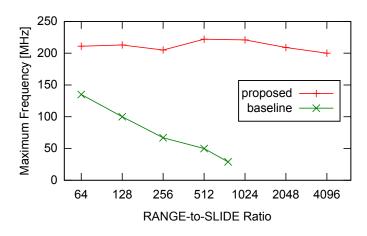

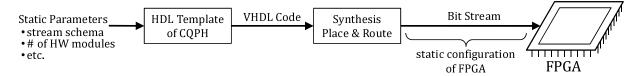

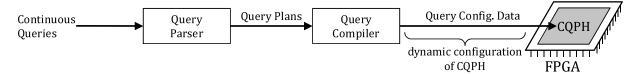

| 5317    | Two-   | phase configuration: static configuration of FPGA (Fig. 5.3.1a) and dynamic con-                       |          |

|         |        | ation of CQPH (Fig. 5.3.1b).                                                                           | 47       |

|         | (a)    | Static Configuration: One-time-only configuration of an FPGA to implement CQPH                         | - 77     |

| (       | (u)    | by using a standard FPGA tool chain. The first phase ( <i>i.e.</i> , static configuration) typ-        |          |

|         |        | ically requires a relatively long period of time. In particular, the compilation steps                 |          |

|         |        | ( <i>i.e.</i> , synthesis and place-and-route) can take on the order of minutes or even up to          |          |

|         |        | hours to complete.                                                                                     | 47       |

| (       | (b)    | Dynamic Configuration: On-the-fly configuration of continuous queries by updat-                        | 47       |

| (       | (0)    | ing internal registers of CQPH at run time. In contrast to the first phase, the second                 |          |

|         |        | phase ( <i>i.e.</i> , dynamic configuration) only requires a very short period of time ( <i>e.g.</i> , |          |

|         |        |                                                                                                        | 47       |

| 5221    | D11    | in the order of microseconds).                                                                         | 47       |

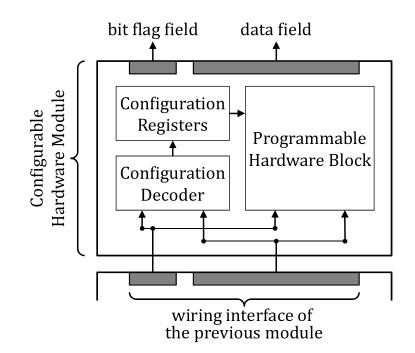

|         |        | k-box view of a configurable hardware module.                                                          | 49<br>50 |

|         |        | Femplate of selection-based filtering.                                                                 | 50       |

|         |        | Femplate of window-based aggregation.                                                                  | 50       |

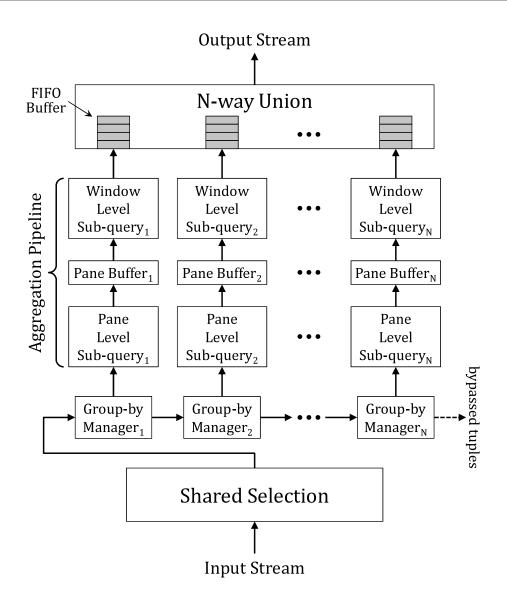

| 5.4.1 ( | Over   | view of the data flow of CQPH Architecture.                                                            | 51       |

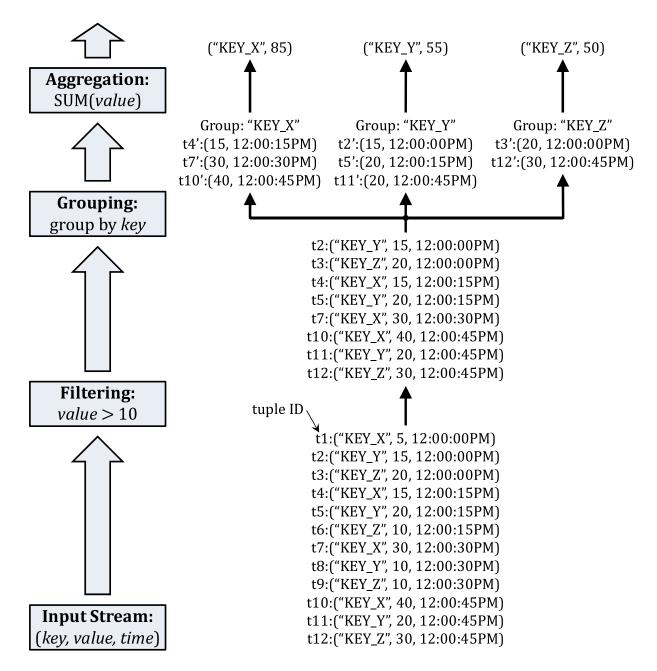

| 5.4.2  | Q7: '          | Given an input stream $KeyValue = \langle key, value, time \rangle$ , first filter out all the tuples      |    |

|--------|----------------|------------------------------------------------------------------------------------------------------------|----|

|        | that d         | o not satisfy the condition in WHERE clause ( <i>i.e.</i> , $value > 10$ ). After that calculate           |    |

|        | the su         | Im of <i>value</i> for each different <i>key</i> for the past <i>1 minute</i> and update the result every  |    |

|        | 1 min          | <i>ute</i> ."                                                                                              | 52 |

| 5.4.3  | An ex          | cample of filtering, grouping, and aggregation operations for Query $Q_7$ for the first                    |    |

|        | windo          | bw (between 12:00:00 and 12:01:00 p.m.)                                                                    | 53 |

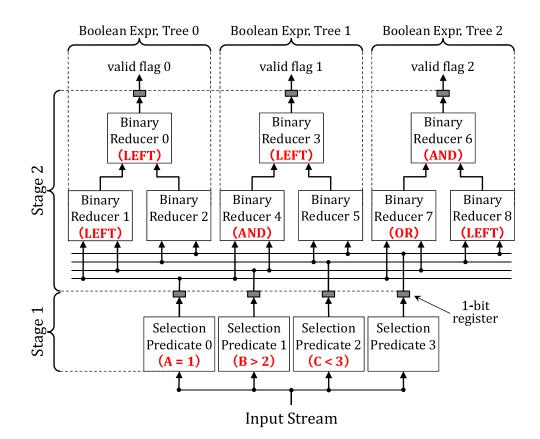

| 5.4.4  | Boole          | an expressions supported by CQPH                                                                           | 54 |

| 5.4.5  | A sim          | plified block diagram of the shared selection module instantiated with the following                       |    |

|        | paran          | neters: (i) # of selection predicate modules = 4 (Stage 1) and (ii) # of Boolean                           |    |

|        | expre          | ssion trees = 3 (Stage 2). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                           | 55 |

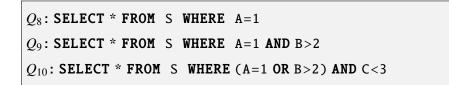

| 5.4.6  | $Q_8 \sim$     | $Q_{10}$ : "Given an input stream $S = \langle A : int, B : int, C : int \rangle$ , select all tuples that |    |

|        | satisf         | y predicates of each query."                                                                               | 55 |

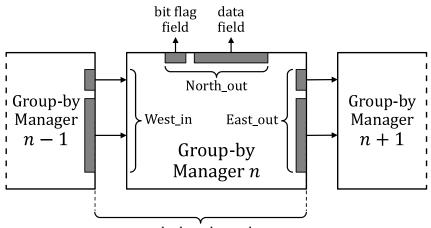

| 5.4.7  | Wirin          | g interface of a Group-by Manager module. Each module accepts its input from                               |    |

|        | West_          | in port and transfers its output to East_out and/or North_out ports                                        | 56 |

| 5.4.8  | Pseud          | lo code of the routing logic for queries with a GROUP-BY clause                                            | 58 |

| 5.4.9  | Simp           | lified version of the routing logic for queries <i>without</i> a GROUP-BY clause                           | 59 |

| 5.4.10 | A sin          | ple example for the group-by operation.                                                                    | 60 |

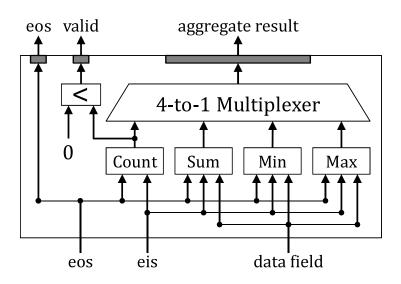

| 5.4.11 | A sin          | plified block diagram of the aggregation module that includes four sub-modules                             |    |

|        | (i.e., a       | aggregate circuits): COUNT, SUM, MIN, and MAX.                                                             | 61 |

| 5.4.12 | Gene           | ration of <i>eis</i> and <i>eos</i> signals for PLQ                                                        | 62 |

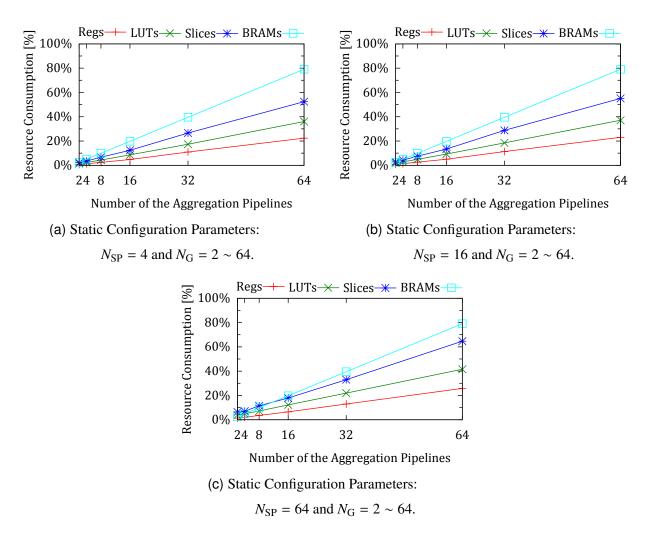

| 5.5.1  | Overa          | all resource consumption of FPGA to implement CQPH with an increasing value of                             |    |

|        | $N_{\rm G} =$  | 2 ~ 64                                                                                                     | 67 |

|        | (a)            | Static Configuration Parameters:                                                                           |    |

|        |                | $N_{\rm SP} = 4$ and $N_{\rm G} = 2 \sim 64$                                                               | 67 |

|        | (b)            | Static Configuration Parameters:                                                                           |    |

|        |                | $N_{\rm SP} = 16 \text{ and } N_{\rm G} = 2 \sim 64.$                                                      | 67 |

|        | (c)            | Static Configuration Parameters:                                                                           |    |

|        |                | $N_{\rm SP} = 64$ and $N_{\rm G} = 2 \sim 64$                                                              | 67 |

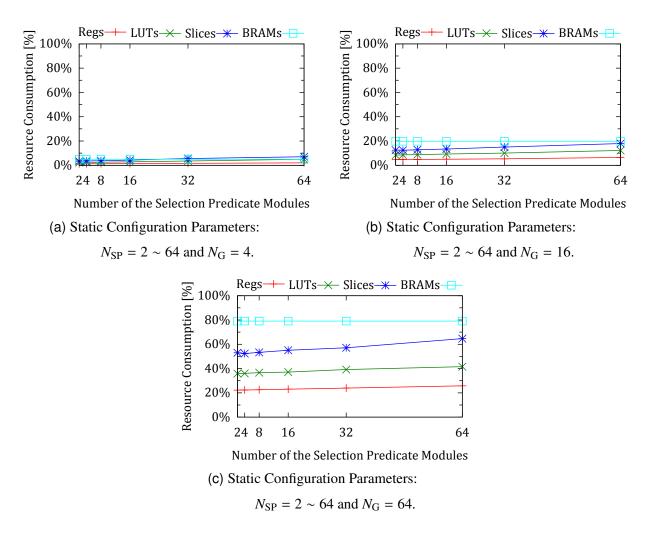

| 5.5.2  | Overa          | all resource consumption of FPGA to implement CQPH with an increasing value of                             |    |

| -      | $N_{\rm SP}$ = | = 2 ~ 64                                                                                                   | 68 |

|        | (a)            | Static Configuration Parameters:                                                                           |    |

|        |                | $N_{\rm SP} = 2 \sim 64$ and $N_{\rm G} = 4$ .                                                             | 68 |

|        | (b)            | Static Configuration Parameters:                                                                           |    |

|        |                | $N_{\rm SP} = 2 \sim 64$ and $N_{\rm G} = 16$ .                                                            | 68 |

|       | (c)        | Static Configuration Parameters:                                                  |    |

|-------|------------|-----------------------------------------------------------------------------------|----|

|       |            | $N_{\rm SP} = 2 \sim 64$ and $N_{\rm G} = 64$                                     | 68 |

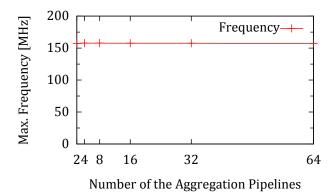

| 5.5.3 | Maxi       | mum clock frequency of CQPH implemented with the following parameters: $N_{SP}$ = |    |

|       | 64 an      | d $N_{\rm G} = 2 \sim 64$                                                         | 69 |

| 5.5.4 | $Q_{11}$ : | Template of a benchmark query for CQPH                                            | 70 |

| 5.5.5 | $Q_{12}$ : | Template of Esper EPL query                                                       | 72 |

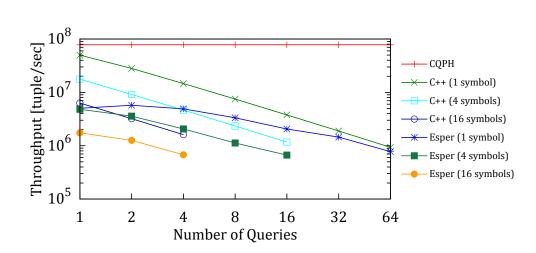

| 5.5.6 | Perfo      | rmance comparison of multi-query execution between HW- and SW-based solutions.    | 72 |

# **List of Tables**

|     |                                                                          | •  |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | Specifications of the Virtex <sup>®</sup> -6 FPGA (XC6VLX240T)           | 20 |

| 3.2 | Number of the window-aggregation modules with respect to the window size | 21 |

| 4.1 | Relation between Original Query, PLQ, and WLQ.                           | 30 |

| 4.2 | Block RAM (BRAM) Utilization.                                            | 42 |

| 5.1 | List of Statically-configured Parameters.                                | 48 |

| 5.2 | Latency and Issue Rate of Each Operation.                                | 64 |

| 5.3 | Dynamic Configuration Time for a Given Query.                            | 65 |

| 5.4 | Specifications of the Kintex <sup>®</sup> -7 FPGA (XC7K325T)             | 66 |

| 5.5 | Static Configuration Parameters.                                         | 66 |

| 5.6 | List of Symbols                                                          | 70 |

| 5.7 | Query Parameters.                                                        | 71 |

# **Chapter 1**

# Introduction

An important and growing class of applications requires to process online data streams on the fly in order to identify emerging trends in a timely manner. Many data processing tasks, such as financial application [23] and traffic monitoring [48], are required to process high-rate data sources with certain time restrictions. To address the issue, database researchers have expanded the data processing paradigm from the traditional "store-and-process" model toward the "stream-oriented processing" model [2, 4, 8].

*Data Stream Management Systems* (DSMSs) [3] deal with potentially infinite streams of data that should be processed for real-time applications, executing SQL-like *continuous queries* [6] over data streams. It is essential for DSMSs that incoming data be processed in real time, or at least near real-time, depending on the applications' requirements. In particular, low-latency and high-throughput processing are key requirements of systems that process unbounded and high-rate data streams rather than fixed-size stored data sets.

One of the key challenges for DSMSs is an efficient support for *sliding-window queries* [5] over unbounded streams. Indeed, it is considered one of the eight key requirements in [41] that a stream processing system must have a highly-optimized and minimal-overhead execution engine to deliver real-time response for high-volume applications. In order to meet the above-mentioned requirement, there is currently a great deal of interest in the potential of using field-programmable gate arrays (FPGAs) as custom accelerators for continuous query processing over data streams [24, 26, 25, 44, 38, 40, 39, 29].

## **1.1 Motivating Issues**

Mueller *et al.* consider the use of FPGAs for data stream processing as co-processors [25]. In particular, they propose an implementation method for sliding-window aggregate queries on an FPGA. In fact, it is a common approach that subsequence of data stream elements (hereafter *tuples*) is defined as a *window*. In other words, windows decompose a data stream into possibly overlapping subsets of tuples (*i.e.*, each

tuple belongs to multiple windows). After that, according to a given query, window-aggregate operators repeatedly calculate aggregate functions such as COUNT, SUM, AVERAGE, MIN, and MAX for each window. Nevertheless, there still remain three practical issues related to the implementation of sliding-window aggregation:

- 1. The first issue is that it is necessary to consider out-of-order arrival of tuples at a windowing operator.

- 2. The second issue is that a large number of overlapping sliding-windows cause severe scalability problems in terms of both performance and area.

- 3. The third issue is that there is a lack of run-time configurability, which severely limits the practical use in a wide range of applications.

Unfortunately, the above issues are neither discussed nor addressed in the previous work [25], and to the best of our knowledge, each of them is still an open question for hardware-based approaches. In the following subsections, a brief explanation is given for each problem.

#### **1.1.1** Out-of-order arrival of tuples

The implementation technique adopted in [25] relies on an implicit assumption about the physical order of incoming tuples, that is to say, tuples arrive in correct order at a windowing operator. Obviously, this assumption simplifies the definition and implementation of sliding windows; however, it does not always fit into a realistic setting where some degree of disorder (*i.e.*, out-of-order arrival of tuples) might be expected.

It is mentioned in [21] that previous works on data streams commonly model a data stream as an unbounded sequence of tuples arriving in order of some timestamp-like attribute; however, disorder naturally occurs in real-world stream systems. This means that, in reality, we cannot always assume all tuples to be ordered by their timestamp values when they arrive to a DSMS. For example, input tuples arriving over a network from remote sources may take different paths with different delays. As a result, some tuples may arrive out of sequence according to their timestamp values.

#### 1.1.2 Scalability issue for overlapping sliding-windows

It is stated in [19] that sliding-window aggregate queries allow users to aggregate input streams at a user-specified granularity and interval, and thereby provide the users a flexible way to monitor streaming data. In other words, user-defined queries can determine the number of overlapping sliding-windows. Nevertheless, the previous approach adopted in [25] relies on a simple replication strategy of aggregation

units for overlapping sliding-windows. As a result, a large number of aggregation circuits are instantiated on an FPGA, and this leads to serious scalability problems in terms of clock frequency (*i.e.*, performance) and hardware resource usage (*i.e.*, area).

#### 1.1.3 Lack of run-time configurability

A common limitation from which the most FPGA-based approaches suffer is that the existing approaches impose significant overhead on run-time query registration/modification. It is mentioned in [29] that while supporting query modification at run time is almost trivial for software-based techniques, they are highly uncommon for custom hardware-based approaches such as FPGAs. Moreover, as stated in [15], given the dynamic environment of data streams, queries can join and leave a streaming system at any time. It is therefore imperative for a query processing accelerator to support on-the-fly configurability for easy adaptation to the dynamic environment.

## 1.2 Objectives

There are three main objectives in this dissertation:

- 1. The first objective is to address the problem of out-of-order arrival of tuples and propose an alternative approach to implement a sliding-window aggregate query on an FPGA.

- 2. The second objective is to address the scalability problem and propose another approach to implement a sliding-window aggregate query on an FPGA in an *efficient* and *scalable* manner.

- 3. The third objective is to address the problem of the lack of run-time configurability and propose a novel query accelerator, namely Configurable Query Processing Hardware (CQPH).

#### **1.2.1** Order-agnostic implementation technique

First, the dissertation presents an order-agnostic implementation of a sliding-window aggregate query on an FPGA, based on a one-pass query evaluation strategy called the *W*indow-*ID* (WID) [20]. With the proposed method, we can process out-of-order tuples at wire speed due to the one-pass query evaluation strategy and simultaneous evaluations of overlapping sliding-windows by taking advantage of the hardware parallelism. The proposed implementation can handle disorder by utilizing punctuations [47]. It is stated in [20] that WID does not require a specific type of assumption about the physical order of tuples in a data stream and can process out-of-order tuples as they arrive without sorting them into the "correct" order. Since the proposed implementation is based on WID approach, it can also process input tuples on the fly without reordering them into the correct order.

#### 1.2.2 Efficient and scalable hardware design

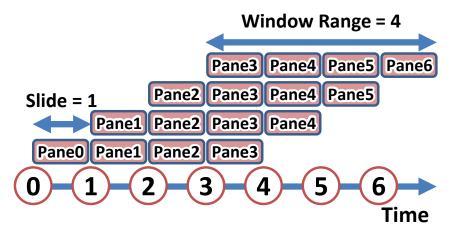

Secondly, the dissertation presents a scalable hardware design of sliding-window aggregation and its implementation on an FPGA, by examining and integrating two key concepts: Pane [19] and Window-*ID* (WID) [20]. Instead of replicating a large number of aggregation modules for overlapping sliding-windows, we divide each sliding window into non-overlapping sub-windows called *panes*. For each sub-window, or pane, we first calculate a sub-aggregate (*i.e.*, pane-aggregate), which is then shared by the aggregation of the multiple windows (*i.e.*, overlapping sliding-windows). The pane-based approach is originally proposed for software-based implementation to reduce the required buffer size and the computation cost [19]. In this work, however, we show that the same idea can provide significant benefits for hardware-based implementation, especially in terms of performance (*i.e.*, the maximum allowable clock frequency), area (*i.e.*, the hardware resource usage), and scalability.

#### 1.2.3 CQPH: Configurable Query Processing Hardware

Finally, the dissertation presents the design and evaluation of Configurable Query Processing Hardware (CQPH), a highly-optimized and minimal-overhead query processing engine, especially designed for sliding-window aggregate queries. CQPH is an FPGA-based query processor that contains a collection of configurable hardware modules, each of which supports selection (*i.e.*, filtering), group-by operation (*i.e.*, partitioning), and sliding-window aggregation. CQPH is highly optimized for performance with a fully pipelined implementation to exploit the increasing degree of parallelism that modern FPGAs support. In addition, the proposed design imposes minimal overhead on query configuration. More specifically, CQPH can support registration of new queries as well as modification of existing queries, without a time-consuming compilation process which is a common drawback of the previous approaches.

## **1.3** Organization of the Dissertation

The rest of the dissertation is organized as follows. Chapter 2 provides necessary background and briefly reviews related work. Chapter 3 presents an order-agnostic implementation of a sliding-window aggregate query on an FPGA. Chapter 4 presents a scalable hardware design of sliding-window aggregation and its implementation on an FPGA. Chapter 5 presents the design and evaluation of CQPH. Finally, Chapter 6 concludes the dissertation by summarizing the results and identifying future work.

# Chapter 2

# **Background and Related Work**

Chapter 2 briefly reviews related work and provides some background information.

## 2.1 Data Processing on FPGAs

#### 2.1.1 Acceleration of Data-intensive Operations using FPGAs

As stated in [45], FPGAs are an increasingly attractive alternative to overcome the architectural limitations of commodity hardware. Mueller *et al.* show the potential of FPGAs as an accelerator for data-intensive operations [24]. It is demonstrated in [24] that FPGAs can achieve competitive performance compared to modern general-purpose CPUs while providing remarkable advantages in terms of power consumption and parallel stream evaluation. Indeed, recently a number of research efforts have used FPGAs to target acceleration of data-intensive workloads. For instance, Putnam *et al.* propose an FPGA-based reconfigurable fabric, called *Catapult*, to accelerate datacenter workloads [37]. They introduce the Catapult fabric into 1,632 servers, and demonstrate its efficacy in accelerating the Bing web search engine. Some other works focus on the idea of using custom hardware to accelerate database queries [49, 9, 10, 53, 52]. Woods *et al.* propose an intelligent storage engine, called *Ibex*, which supports advanced SQL off-loading [49]. Dennl *et al.* propose partial reconfiguration-based approach to accelerate a subset of SQL queries for traditional database systems [9, 10]. Yoshimi *et al.* present acceleration of OLAP workload on interconnected FPGAs with flash storage [53, 52].

#### 2.1.2 Continuous Query Processing on FPGAs

FPGAs are used to process data streams due to their low-latency and high-throughput processing advantages. Most of the previous FPGA-based approaches require full circuit compilation to implement dedicated hardware for different kinds of query workloads. In general, these query-tailored circuits are inherently very efficient in terms of performance, area and power consumption; however, static compilation process is highly CPU-intensive and imposes significant overhead on dynamic workload changes. For example, Sadoghi *et al.* propose an efficient event-processing platform called *fpga-ToPSS* [38], and demonstrate high-frequency and low-latency algorithmic trading solutions [40]. These projects mainly focus on queries with selection operator.

#### Window Joins

How to implement stream joins on FPGAs is indeed a challenging task. It is mentioned in [44] that the M3Join proposed by Qian *et al.* [7] implements the join step as a single parallel lookup; however, this approach causes the significant performance drop for larger join windows. Alternatively, another study [39] concentrates on the execution of SPJ (Select-Project-Join) queries with multi-query optimization. Terada *et al.* suggest another approach to implement window join operator on an FPGA [43]. Nevertheless, only two join processes are concurrently executed since their approach is based on sequential execution.

To address the issue, Teubner and Mueller propose a new join algorithm called *handshake join* [44]. Data flow model of handshake join does not suffer from the limitation mentioned above and the previous study such as [30, 31, 32, 33] focus on the acceleration of handshake join on FPGA. Finally, Kung and Leiserson propose the idea of *systolic array* that is a structure composed of an array of processors for VLSI implementation [18]. It is stated in [18] that processing units of a systolic array rhythmically compute and pass data through the system. The data processing and communication model of *join cores* [30, 31, 32, 33] are consistent with the properties of systolic arrays. In fact, the data flow model of the handshake join is very similar to the join arrays proposed for relational databases [17].

#### Glacier: A query-to-hardware compiler

An important study closely related to this work is *Glacier* [25, 26]. Mueller *et al.* propose a query-tohardware compiler, called Glacier, for continuous queries [25]. The compiler takes a query plan as its input and produces VHDL description of a logic circuit that implements the input plan. In particular, it provides a library of components for basic operators such as selection, aggregation, grouping, and windowing operators. Glacier can generate logic circuits by composing the library components on an operator-level basis, and thereby can support a wide range of continuous queries involving the basic operators (*i.e.*, selection, aggregation, grouping, and windowing operators). The windowing operator provides sliding-window functionality and aggregate operator includes four distributive (*i.e.*, COUNT, SUM, MIN, and MAX) and an algebraic (*i.e.*, AVERAGE) aggregate functions [14]. As windowing and aggregation operators are provided by the library, Glacier can compile sliding-window aggregate queries into hardware circuits to be implemented on an FPGA. As described in Chapter 1, there are three issues regarding the sliding-window aggregate queries implemented by Glacier:

- out-of-order arrival of tuples,

- · scalability issue for overlapping sliding-windows, and

- lack of run-time configurability.

In the following chapters, three alternative approaches are presented in detail to address each issue.

#### 2.1.3 Run-time Configuration of FPGAs

Most of the previous FPGA-based approaches suffer from a common limitation, namely, lack of flexibility to adapt to dynamic workload changes. One possible solution is to exploit partial reconfiguration technology of FPGAs along with prebuilt libraries of custom-designed components. For example, Dennl *et al.* [9, 10] propose partial reconfiguration-based approach to accelerate a subset of SQL queries for traditional database systems. It is stated, however, in [46] that the partial reconfiguration causes another level of complexity which severely limits its use in real-world systems.

Another promising solution is the approach adopted in *skeleton automata* [45, 46] or *Flexible Query Processor* (FQP) [29, 27, 28]. The main idea is to implement a generic template circuit along with a number of configuration registers/memories. With this approach, the template circuit can be easily configured for a specific type of workloads by changing the values of the configuration registers/memories within the template design. For instance, the skeleton automata and FQP can support XML projections and sliding-window join queries, respectively. The major advantage of both works is that they can offer run-time configurability without long running static compilation or the partial reconfiguration. CQPH shares similar motivation with skeleton automata and FQP; however, target workloads are quite different. The main focus of the dissertation differs from these works as we are primarily concerned with sliding-window aggregate queries which are not in the scope of [45, 46, 29].

## 2.2 Sliding-Window Aggregation

### 2.2.1 Example of a sliding-window aggregate query

Consider the following online auction example taken from Li *et al.* [19]. In this example, an online auction system monitors bids on auction items. We assume an input stream that contains information about each bid, the schema of which is defined as  $\langle item-id, bid-price, timestamp \rangle$ . In addition, assume that the online auction system runs over the Internet, and each bid is streamed into a central auction

```

SELECT max(bid-price), timestamp

FROM bids [RANGE 4 minutes

SLIDE 1 minute

WATTR timestamp]

```

Figure 2.2.1:  $Q_1$ : "Find the maximum bid-price for the past 4 minutes and update the result every 1 minute."

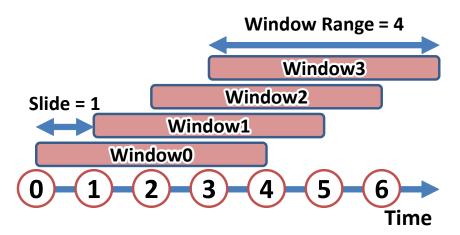

server where a DSMS is running. Query  $Q_1$  (cited from [19]) shows an example of a sliding-window aggregate query (see Fig. 2.2.1). This query can be used to find the maximum bid-price for the past 4 minutes and update the result every 1 minute.

#### Window specification

It is stated in [5] that since data streams are infinite, queries that execute over a data stream need to define a region of interest (termed a window). Following the definition of window semantics [20], Query  $Q_1$ introduces a window specification which consists of a window type and a set of parameters that define a window. In Query  $Q_1$ , *sliding windows* have three parameters: *RANGE*, *SLIDE*, and *WATTR*. *RANGE* indicates the size of the windows; *SLIDE* indicates the step by which the windows move; *WATTR* indicates the windowing attribute—the attribute over which *RANGE* and *SLIDE* are specified [20].

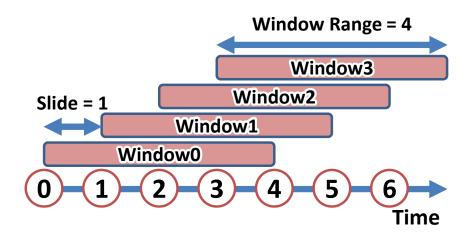

It is important to note that the window specification can be user-defined values; therefore, as stated in [19], sliding-window aggregate queries allow users to aggregate the stream at a user-specified granularity (*i.e.*, *RANGE*) and interval (*i.e.*, *SLIDE*). Given the specification above, for example, the bid stream is divided into overlapping 4-minute windows starting every minute, based on the timestamp attribute of each tuple. Fig. 2.2.2 illustrates overlapping sliding-windows (only the first four windows) for Query  $Q_1$ . Notice that all windows in Fig. 2.2.2 have *RANGE* = 4 and *SLIDE* = 1, respectively.

#### **Output generation**

Window-aggregate operators are generally classified as a blocking operator in DSMSs; therefore, it is necessary to unblock them at the end of each window. One of the common approaches for DSMSs to unblock aggregate operators is to use timestamp attribute of each tuple. For example, in Query  $Q_1$ , a MAX aggregate operator can keep track of timestamp values of input tuples (*i.e.*, bids) to identify the end of each sliding-window. In this case, the maximum value of bid-price can be calculated at the end of each window and Query  $Q_1$  produces an output tuple with schema (*max, timestamp*) where the timestamp attribute specifies the end of the window. For interested readers, some key applications of

Figure 2.2.2: Overlapping Sliding-Windows for Query  $Q_1$  (*RANGE* = 4 minutes and *SLIDE* = 1 minute).

sliding-window queries are discussed in [5].

#### 2.2.2 Handling out-of-order arrival of tuples

Abadi *et al.* [2] classifies types of operators as *order-agnostic* or *order-sensitive*. Order-agnostic operators can always process tuples in the order in which they arrive whereas order-sensitive operators can only be guaranteed to execute with finite buffer space and in finite time if they can assume some ordering (potentially with bounded disorder) over their input streams [2].

#### Window-ID (WID)

Li *et al.* presents a software-based implementation of order-agnostic window aggregation [20]. Their approach is called Window-*ID* (WID), and it is stated in [21] that WID provides a method to implement window aggregate queries in an order-agnostic way, by using special annotations called *punctu-ations* [47]. Informally, a punctuation can be regarded as a special tuple that contains some meta-data about a given stream. For instance, punctuations can be used to indicate that no more tuples having certain timestamp values will be seen in the stream [20]. In practice, punctuation tuples are embedded into a data stream, and those tuples can be used to unblock some blocking operators such as group-by and aggregation.

#### **Slack Specification**

Another approach to handle disorder is to use *slack* specification. Slack [2] defines an upper bound on the degree of disorder which can be handled by an operator. As mentioned before, we cannot expect that

all tuples always arrive in order of some timestamp-like attribute in a realistic setting. Instead, Aurora [2] assumes some ordering (potentially with bounded disorder) over input streams. Any tuple arriving after its corresponding period specified by a slack parameter is discarded. In Aurora, the slack parameter is used to specify the number of tuples to be stored and sorted before an order-sensitive operator processes input tuples. Aurora classifies window aggregation as an order-sensitive operation. In Aurora, therefore, aggregate operators require buffering and reordering of tuples before computation in order to handle disorder.

# Chapter 3

# Sliding-window Aggregate Operator over Out-of-order Data Streams

## 3.1 Abstract

This chapter presents the design and evaluation of an FPGA-based accelerator for sliding-window aggregation over data streams with out-of-order data arrival. We propose an order-agnostic hardware implementation technique for windowing operators based on a one-pass query evaluation strategy called Window-ID, which is originally proposed for software implementation. The proposed implementation succeeds to process out-of-order data items, or tuples, at wire speed due to the simultaneous evaluations of overlapping sliding-windows. In order to verify the effectiveness of the proposed approach, we have also implemented an experimental system as a case study. Our experiments demonstrate that the proposed accelerator with a network interface achieves an effective throughput around 760 Mbps or equivalently nearly 6 million tuples per second, by fully utilizing the available bandwidth of the network interface.

## **3.2 Design Concept**

Although Glacie [25] is capable of compiling sliding-window aggregate queries into logic circuits, it implements a windowing operator as an order-sensitive operator. In other words, its implementation relies on an implicit assumption about the physical order of incoming tuples; that is to say, tuples arrive in correct order at the windowing operator. Obviously, this assumption simplifies the definition and implementation of sliding windows; however, it does not always fit into a realistic setting where some degree of disorder can be expected. Glacier does not discuss the issue regarding out-of-order arrival of tuples.

# CHAPTER 3. SLIDING-WINDOW AGGREGATE OPERATOR OVER OUT-OF-ORDER DATA STREAMS

In order to address the problem, this dissertation proposes an alternative implementation technique for sliding-window aggregate queries. The proposed implementation follows the same approach as WID [20] to handle disorder. In other words, aggregation operation is order-agnostic, and punctuations are used to unblock window-aggregate operators. On the other hand, WID is proposed for a software-based implementation. The main interests of WID [20] are to calculate window aggregates with the one-pass evaluation strategy and to handle disorder by using punctuations. However, hardware-based implementation of order-agnostic window aggregation is neither provided nor discussed in [20].

Contrary to the software-based implementation proposed in [20], this dissertation presents hardwarebased implementation which handles multiple windows with a single clock cycle. The proposed implementation instantiates multiple window-aggregation modules by taking advantage of hardware parallelism. Upon arrival of a new tuple, each of the window-aggregation modules can simultaneously evaluate the tuple within the same clock cycle. This is the main difference between software-based WID [20] and our proposed approach.

The number of the window-aggregation modules is determined by using window parameters (*RANGE* and *SLIDE*) and a slack [2] specification. As mentioned in Chapter 2, Aurora [2] uses a slack parameter to determine the number of tuples to be buffered and reordered before aggregation. The proposed approach, however, relies on punctuations to handle disorder, and the slack parameter is used to calculate the number of the window-aggregation modules required to be instantiated. This is a significant difference between the approach adopted in this work and that of Aurora.

# 3.3 Motivating Application

Glacier [25] demonstrates how to implement a window aggregate query on an FPGA. For example, the implementation of the third query of [25] includes a windowing operator which implicitly relies on the arrival sequence of input tuples. Contrary to Glacier, the proposed approach permits windowing on any attribute, allowing a bounded disorder of the tuples. This work focuses on the same query (*i.e.*, the third query of [25]) as a case study and shows how to implement the query in an order-agnostic manner. It should be noted that the proposed approach is general enough to apply a wide range of window aggregate queries which include the primitive aggregate functions such as COUNT, SUM, AVERAGE, MIN, and MAX (*i.e.*, the same aggregate functions supported by Glacier).

This work assumes the same financial application as that of the previous work [25]. Our approach, however, requires an explicit timestamp attribute to define windows over an input stream. Instead of a simple sequence number considered in [25], a timestamp attribute has been added to the schema of the input stream. The schema of the stream, called *Trades*, is defined in Fig. 3.3.1. This schema describes the structure of an input tuple. Each tuple of the stream consists of four attributes (*i.e.*, Symbol, Price,

```

CREATE INPUT STREAM Trades(

Symbol char[4], -- valor symbol

Price int, -- stock price

Volume int, -- trade volume

Time int) -- timestamp

```

Figure 3.3.1: The schema of the input stream. Each tuple of the stream consists of four attributes: Symbol, Price, Volume, and Time.

```

SELECT Time, count(*) AS Number

FROM Trades [RANGE 600 seconds

SLIDE 60 seconds

WATTR Time]

WHERE Symbol = "UBSN"

```

Figure 3.3.2:  $Q_2$ : "Count the number of trades of UBS (Union Bank of Switzerland) shares for the past 10 minutes (600 seconds) and update the result every 1 minute (60 seconds)."

Volume, and Time) each of which is represented as a 32-bit value. Based on the definition of window semantics [20], the example query can be written as in Fig. 3.3.2.

In Query  $Q_2$ , WATTR indicates the windowing attribute (*i.e.*, Time) over which RANGE and SLIDE are specified. Given the window specification of Query  $Q_2$ , the input stream is divided into overlapping 10-minute windows starting every minute, based on the *Time* attribute of each tuple. For each window,  $Q_2$  counts the number of tuples which satisfy the condition (*i.e.*, WHERE Symbol = "UBSN"), and it generates an output stream with schema  $\langle Time, Number \rangle$  where the *Time* attribute indicates the end of the window. The details of the implementation of Query  $Q_2$  are provided in the following section.

## **3.4 Implementation Details**

#### 3.4.1 Wiring Interface

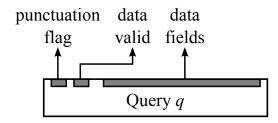

In this work, the same wiring interface as that of the previous work [25] is adopted to represent data flow. That is to say, each *n*-bit-wide data is regarded as a set of *n* parallel wires. Furthermore, additional *punc*-*tuation flag* and *data valid* lines each of which is a one-bit signal indicate the presence of a punctuation and a tuple, respectively. For example, datum on the multiple lines (*i.e.*, *n* parallel wires) is considered

Figure 3.4.1: Wiring Interface for a query q.

as a punctuation when their *punctuation flag* is asserted (*i.e.*, set to logic "1"). Similarly, the data lines are regarded as a tuple when their *data valid* field is asserted.

Following the notation of [25], Fig. 3.4.1 shows a black box view of the hardware implementation for a given query *q*. In Fig. 3.4.1, the gray-shaded boxes represent flip-flop registers. It is mentioned in [25] that their circuits are all clock-driven (*i.e., synchronized*), and each operator writes its output into a flip-flop register after processing. The present work follows the same approach and implements a fully pipelined hardware for the sliding-window aggregate query.

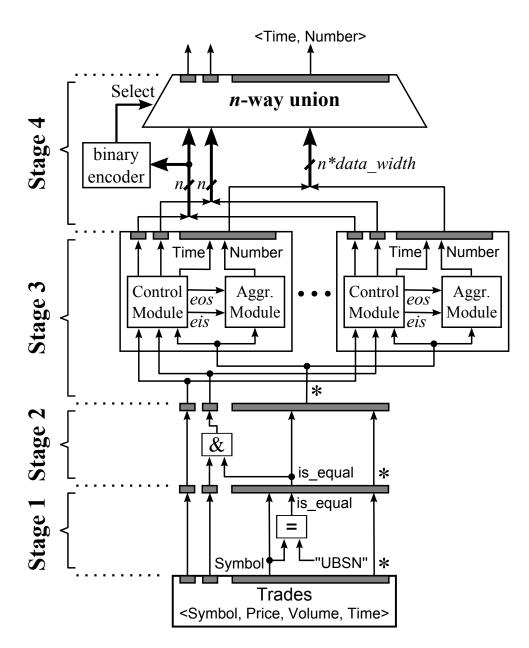

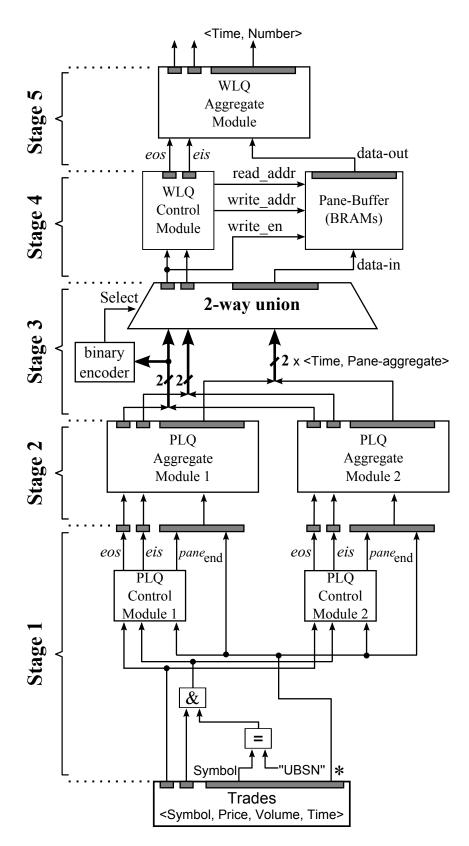

## 3.4.2 Hardware Execution Plan

Hardware execution plan for Query  $Q_2$  is illustrated in Fig. 3.4.2. As shown in Fig. 3.4.2, the proposed implementation adopts a 4-stage pipeline architecture. Intermediate results are stored into flip-flop registers (*i.e.*, the gray-shaded boxes) at the end of the each stage. In other words, these registers can be regarded as pipeline registers, and each stage of the pipeline can use the result of the previous stage. It should be noted that each stage requires only one clock cycle to complete. The arrows indicate the connections between the pipeline stages, as well as between hardware components. According to the notation adopted in the previous work [25], name of a specific field in the *data fields* is explicitly identified with its label wherever appropriate. It should be also mentioned that the label "\*" means "all of the remaining fields" in the data bus.

### **Selection Operation**

The beginning two stages of Fig. 3.4.2 correspond to a selection operation. In **Stage 1**, *Symbol* field of the data bus is compared to a constant value ("UBSN") which is specified in the WHERE expression of Query  $Q_2$  (indicated as  $\equiv$  in Fig. 3.4.2). At the same time, the result of the comparison is labeled as a one-bit *is\_equal* flag and added to the data bus. In **Stage 2**, a logical AND gate (indicated as & in Fig. 3.4.2) computes whether an input tuple is valid or not. If the tuple should be discarded, the *data valid* flag is negated (*i.e.*, set to logic "0") for the next pipeline stage. Actually, these two stages can be

# CHAPTER 3. SLIDING-WINDOW AGGREGATE OPERATOR OVER OUT-OF-ORDER DATA STREAMS

Figure 3.4.2: Hardware execution plan for Query  $Q_2$ .

implemented in a straightforward way based on the approach proposed in the previous work [25]. The main difference, however, is the presence of the *punctuation flag* field which is required for **Stage 3**. It is stated in [20] that some operators, such as selection, simply pass punctuations through to the next operator in a query plan. **Stage 1** and **Stage 2** meet the above requirement since *punctuation flag* field is directly connected to the next stage of the pipeline as shown in Fig. 3.4.2.

Window-Aggregation Module

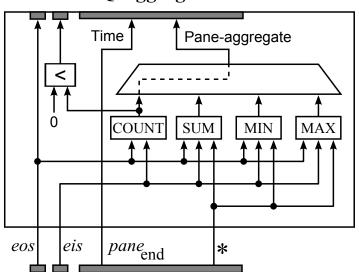

Figure 3.4.3: Block diagram of a window-aggregation module.

#### Windowing and Aggregation

The next step is **Stage 3** of the pipeline which corresponds to windowing and aggregation operators. In **Stage 3**, a number of window-aggregation modules are instantiated as shown in Fig. 3.4.2. They provide sliding-window functionality and can concurrently compute aggregate functions. The number of window-aggregation modules to be instantiated is calculated by using *RANGE*, *SLIDE*, and *SLACK* parameters (see the following Equation 3.4.1 and 3.4.2).

$$N_{\text{WIN}} = \left[\frac{RANGE}{SLIDE}\right] + x, \text{ where } x \in \mathbb{Z}^+$$

(3.4.1)

$$x \ge \frac{SLACK + RANGE}{SLIDE} - \left\lceil \frac{RANGE}{SLIDE} \right\rceil$$

(3.4.2)

We should determine the number of the window-aggregation modules required to handle disorder specified by a slack parameter. For example, assume that *SLACK* value is set to 60 seconds for Query  $Q_2$ . Recall from Query  $Q_2$  that window parameters are specified as RANGE = 600 seconds and SLIDE = 60 seconds, respectively. Applying Equation 3.4.2, we obtain  $x \ge \frac{60+600}{60} - \left\lceil \frac{600}{60} \right\rceil \Rightarrow x \ge 1$ . After that, using Equation 3.4.1 with x = 1, we can calculate  $N_{WIN} = \left\lceil \frac{600}{60} \right\rceil + 1 \Rightarrow N_{WIN} = 11$ .

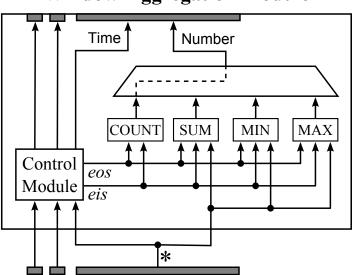

**Aggregation Module.** Each instance of window-aggregation module consists of *aggregation module* and *control module* as shown in **Stage 3** of Fig. 3.4.2. A more detailed block diagram of a single window-

aggregation module is depicted in Fig. 3.4.3. It is stated in [25] that primitive aggregate functions such as COUNT, SUM, AVERAGE, MIN, and MAX can be implemented in a straightforward fashion on an FPGA. Glacier [25] supports the above five aggregate functions, and in this work, we also focus on the same aggregate operators. In fact, AVERAGE can be obtained with the combination of two aggregate values: SUM and COUNT. It is therefore necessary to implement the other four aggregate operators as shown in Fig. 3.4.3. When it comes to the implementation of Query  $Q_2$ , a standard counter component can be used inside the aggregation module. Since Query  $Q_2$  requires count(\*) function, the result of the COUNT operator is selected as the output value (indicated as the broken line in Fig. 3.4.3).

Aggregation module maintains partial aggregates and only stores the current (partial) result of aggregation instead of buffering all input tuples belonging to the current window. In other words, it incrementally computes the aggregate result as new tuples arrive and always keeps the latest result. In order to maintain the aggregate value, it requires two control signals: enable input stream (*eis*) and end of stream (*eos*). These signals are provided by the control module as illustrated in Fig. 3.4.3. Both *eis* and *eos* are asynchronous signals each of which is a one-bit flag. The *eis* signal indicates whether or not datum on the *data fields* should be considered as a valid tuple for the current window. Whenever *eis* is asserted, the aggregation operator accepts input tuple and records its contribution to the partial result. If *eis* is negated, the aggregation operator simply ignores the input data and waits for the next tuple to arrive. The other signal, *eos*, indicates whether an input stream reaches the end of the current window. When *eos* is asserted, it means that the current window is no longer active, and the aggregate operator should reset its internal state to be ready for input tuples belonging to the next window.

**Control Module.** Each control module maintains its own window states and provides two control signals (*i.e.*, *eis* and *eos*) to the aggregation module. The control module maintains window states by updating its internal registers called *win*<sub>begin</sub> and *win*<sub>end</sub>. These registers represent the beginning and the end of the current window, respectively. The control module uses  $win_{begin}$  and  $win_{end}$  registers to generate the two control signals, *eis* and *eos*. Details about how to maintain these registers and to generate the control signals are provided in Algorithm 1 and Algorithm 2, respectively.

Algorithm 1 describes how to initialize  $win_{begin}$  and  $win_{end}$  registers. Recall from Query  $Q_2$  that windowing attribute (*i.e.*, WATTR) is specified as TIME. Therefore, WATTR<sub>start</sub> can be considered as TIME<sub>start</sub> which means the start time of the execution of the query. It can be determined in several ways. For example, if one knows when to start the query (*e.g.*, market opening times for Query  $Q_2$ ), this information can be used to determine  $TIME_{start}$  value. Another option is to use the most recent value of the punctuation. One can also use the timestamp value of the first tuple with the SLACK parameter (*e.g.*,  $TIME_{start} = TIME_{first tuple} - SLACK$ ). The other parameters (*i.e.*,  $N_{WIN}$ , RANGE, SLIDE) can be determined before the execution of the query; thus, they are regarded as constant parameters.

### Algorithm 1 Maintain window states (winbegin and winend)

#### **State Registers:**

win<sub>begin</sub>(i): the beginning of the *i*-th window instance win<sub>end</sub>(i): the end of the *i*-th window instance

#### Initialization:

for all *i* such that  $1 \le i \le N_{WIN}$  do

$win_{begin}(i) \leftarrow WATTR_{start} + (i-1) \times SLIDE$  $win_{end}(i) \leftarrow WATTR_{start} + (i-1) \times SLIDE + RANGE$

#### end for

#### **Synchronous Update:**

for all *i* such that  $1 \le i \le N_{WIN}$  do for each clock cycle do if punctuation flag is asserted and  $WATTR \ge win_{end}(i)$  then  $win_{begin}(i) \leftarrow win_{begin}(i) + N_{WIN} \times SLIDE$  $win_{end}(i) \leftarrow win_{end}(i) + N_{WIN} \times SLIDE$ end if end for end for

In addition to initialization, Algorithm 1 shows the update operation of the registers. Initialization or update operation described in Algorithm 1 can be completed in one clock cycle. It should be emphasize that the control module included in each window instance has its own window states. Notice that  $win_{begin}(i)$  and  $win_{end}(i)$  are correspond to the *i*-th window instance. All window instances concurrently perform the same operation on each cycle in a synchronous manner.

The generation of the asynchronous control signals is described in Algorithm 2. Notice that eis(i) and eos(i) are correspond to the *i*-th window instance. The control module included in each window instance generates these signals, using its own window states as well as input signals. It is important to notice that the implementation of eis(i) and eos(i) signals is fully asynchronous. The aggregation module can use the control signals as soon as they are generated within the same clock cycle. In other words, all of the operations performed in both the control module and the aggregation module can be completed in a single clock cycle.

```

eis(i): input enable signal for the i-th window instance

eos(i): output enable signal for the i-th window instance

Asynchronous Update:

for all i such that 1 \le i \le N_{WIN} asynchronously do

if punctuation flag is negated then

negate eos(i) signal

if data valid is asserted and

win_{begin}(i) \le WATTR < win_{end}(i) then

assert eis(i) signal

else

negate eis(i) signal

end if

else {punctuation flag is asserted}

negate eis(i) signal

if WATTR \ge win_{end}(i) then

assert eos(i) signal

else

negate eos(i) signal

end if

end if

end for

```

Algorithm 2 Generate asynchronous signals (*eis* and *eos*)

**Asynchronous Signals:**

### **Union Operation**

It is stated in [25] that, from a data flow point of view, the task of an algebraic union operator is to merge the outputs of several source streams into a single output stream. As shown in Fig. 3.4.2, the *n*-way union operator merges the outputs of *n* window-aggregation modules and generates a single result stream.

The implementation of the union operator is based on a multiplexer component. According to a select signal, the multiplexer component transfers the result of *i*-th window-aggregation module to the output registers of **Stage 4**. As illustrated in Fig. 3.4.2, the select signal is provided by a binary encoder component. It should be also mentioned that **Stage 4** requires only one clock cycle to complete its operation.

| # of Slice Registers | 301,440 |

|----------------------|---------|

| # of Slice LUTs      | 150,720 |

| # of Slices          | 37,680  |

| # of BRAM (36Kbit)   | 416     |

Table 3.1: Specifications of the Virtex<sup>®</sup>-6 FPGA (XC6VLX240T).

Glacier [25] evaluates the complexity and performance of the resulting circuits in terms of *latency* and *issue rates*. Issue rate is defined as the number of tuples that can be processed per clock cycle. The overall latency and the issue rate of the proposed implementation are 4 cycles and 1 tuple/cycle, respectively.

## 3.5 Evaluation

The proposed design is implemented on a Virtex<sup>®</sup>-6 FPGA (XC6VLX240T) included in the Xilinx ML605 Evaluation Kit [51]. The specification of the FPGA used to implement the design is given in Table 3.1. Xilinx ISE 14.7 is used as an FPGA development environment during the implementation process (*e.g.*, synthesis, map, and place & route).

### 3.5.1 Resource Utilization and Performance

In order to evaluate the resource utilization and performance of the proposed design, Query  $Q_2$  is implemented with different sizes of sliding windows. The *RANGE* of a window is increased from 10 minutes to 60 minutes, by increments of 10 (*i.e.*, a total of six different configurations). It should be also noted that all of the implemented queries have the same *SLIDE* parameter as Query  $Q_2$  (*i.e.*, 60 seconds). A baseline design is implemented with *SLACK* = 0 as a reference point and the proposed design is implemented with *SLACK* = 60, respectively. Each design is synthesized with a timing constraint of 6.37 ns, which yields the target clock frequency of 157 MHz.

## **Resource Utilization**

The circuit size of each design is measured in terms of the number of slice registers, the number of slice LUTs (Look-Up Tables), and the number of occupied slices. The resource usage is expected to increase with respect to the number of the window-aggregation modules instantiated on the target device. The number of these modules can be easily calculated by Equation 3.4.1 and Equation 3.4.2, using *RANGE*,

|                          |           |        | Size of the Time-based Sliding Window ( <i>i.e.</i> , <i>RANGE</i> ) |                                 |                                              |                                     |                                        |  |

|--------------------------|-----------|--------|----------------------------------------------------------------------|---------------------------------|----------------------------------------------|-------------------------------------|----------------------------------------|--|

|                          |           | 10 min | 20 min                                                               | 30 min                          | 40 min                                       | 50 min                              | 60 min                                 |  |

| aseline ( $SLACK = 0$ )  | :         | 10     | 20                                                                   | 30                              | 40                                           | 50                                  | 60                                     |  |

| coposed ( $SLACK = 60$ ) | :         | 11     | 21                                                                   | 31                              | 41                                           | 51                                  | 61                                     |  |

|                          | · · · · · |        | aseline $(SLACK = 0)$ : 10                                           | aseline ( $SLACK = 0$ ) : 10 20 | aseline ( <i>SLACK</i> = 0) : $10 \ 20 \ 30$ | aseline $(SLACK = 0)$ : 10 20 30 40 | aseline $(SLACK = 0)$ : 10 20 30 40 50 |  |

Table 3.2: Number of the window-aggregation modules with respect to the window size.

(a) Baseline implementation with SLACK = 0. (b) Proposed implementation with SLACK = 60.

Figure 3.5.1: Overall resource consumption as a percentage of the total available resources on the target FPGA (Xilinx XC6VLX240T) with respect to the window size (*i.e.*, *RANGE*).

*SLIDE*, and *SLACK* parameters. For a reference, Table 3.2 summarizes the number of the window-aggregation modules for both *baseline* (*SLACK* = 0) and *proposed* (*SLACK* = 60) implementations.

Overall resource consumption is plotted in Fig. 3.5.1. The x-axes of Fig. 3.5.1a and Fig. 3.5.1b represent the size of the time-based sliding window (*i.e.*, *RANGE*) from 10 to 60 minutes. The y-axes of the same figures indicate the resource consumption as a percentage of the total available resources on a Xilinx XC6VLX240T FPGA device. As shown in Fig. 3.5.1a or Fig. 3.5.1b, all three graphs (*i.e.*, Slice Registers, Slice LUTs, and Occupied Slices) are almost linearly increased with increasing window size, as expected. The increase in window size results in a higher  $\frac{RANGE}{SLIDE}$  ratio. This implies an increase in the number of the window-aggregation modules (see Table 3.2). This is the main reason for the increased resource utilization. It should be also emphasized that a relatively small percentage of the overall FPGA resources is required to implement the query. For example, when the size of window is 10 minutes, slice usage is particularly low (less than 2%) for both baseline (*SLACK* = 0) and proposed (*SLACK* = 60) implementations. Even if the size of window is increased up to 60 minutes, overall slice utilization is

# CHAPTER 3. SLIDING-WINDOW AGGREGATE OPERATOR OVER OUT-OF-ORDER DATA STREAMS

(a) Comparison of the number of registers.

(b) Comparison of the number of LUTs.

(c) Comparison of the number of slices.

Figure 3.5.2: Comparison of the resource usage between the baseline implementation (SLACK = 0) and the proposed implementation (SLACK = 60).

still less than 9%.

In order to evaluate the resource overhead of the proposed design, Fig. 3.5.2 summarizes the results of the comparison of the hardware-resource usage between the baseline implementation and the proposed implementation. The x-axes of Fig. 3.5.2a (registers), Fig. 3.5.2b (LUTs), and Fig. 3.5.2 (slices) represent the size of the time-based sliding window (*i.e.*, *RANGE*) from 10 to 60 minutes. The y-axes of the same figures indicate the actual number of each resource (*i.e.*, registers, LUTs, or slices) required to implement the design on the target FPGA device. Results indicate that the proposed implementation does not impose significant overhead on the resource usage over the baseline implementation. More specifically, the overhead is only a few percent of the total available resources on the target FPGA device. This means that the proposed implementation can handle a disordered stream (*SLACK*  $\leq$  60 seconds) with a very reasonable hardware cost.

# CHAPTER 3. SLIDING-WINDOW AGGREGATE OPERATOR OVER OUT-OF-ORDER DATA STREAMS

(a) Baseline implementation with SLACK = 0.

(b) Proposed implementation with SLACK = 60.

Figure 3.5.3: Maximum clock frequencies of the implemented design on the target FPGA (Xilinx XC6VLX240T) with respect to the window size (*i.e.*, *RANGE*).

#### **Performance Evaluation**

The performance of the implemented design is evaluated in terms of the maximum clock frequency of the circuit for each window size. The clock frequency can be obtained from post-place & route static timing report, which is provided by Xilinx's Timing Analyzer tool. The obtained results are summarized in Fig. 3.5.3 for baseline (*SLACK* = 0) and proposed (*SLACK* = 60) implementations, respectively. The x-axes of Fig. 3.5.3a and Fig. 3.5.3b represent the size of the time-based sliding window (*i.e.*, *RANGE*) from 10 to 60 minutes. The y-axes of the same figures indicate the maximum clock frequencies of the implemented design on the target FPGA device.

As shown in Fig. 3.5.3a and Fig. 3.5.3b, each implementation achieves the target clock frequency of 157 MHz. Equivalently, this means that all implementations meet the timing constraint of 6.37 ns. Since the issue rate of the implemented queries is equal to 1 tuple/cycle, the proposed implementation can process up to 157 million tuples per second for different sizes of windows. It is also important to note that we obtained almost the same results for both baseline and proposed implementations as indicated in Fig. 3.5.3a and Fig. 3.5.3b. This means that an additional window-aggregation module of the proposed implementation does not impose any overhead on the performance of the overall circuit.

We can calculate the peak throughput by multiplying the data width of an input tuple by the clock frequency. Recall that the data width of a tuple is 128 bits; therefore, multiplying 157 million tuples/s by 128 bits/tuple yields 20,096 Mbps. Thus, the peak throughput can be estimated at 20 Gbps. As for latency, recall that the latency of the implemented queries is equal to 4 cycles, and the clock period is 6.37 ns if we assume a clock rate of 157 MHz. Hence, multiplying 4 by 6.37 ns yields 25.48 ns. These data lead us to the conclusion that the proposed approach can accomplish both high throughput (over 150

Host computer

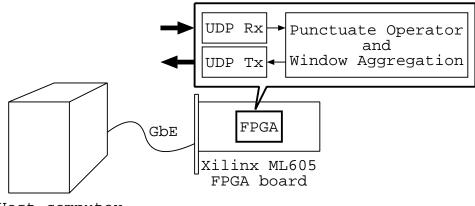

Figure 3.5.4: Overview of the Experimental System.

million tuples per second) and low latency (the order of a few tens of nanoseconds) which are essential for stream processing systems to handle a huge volume of data for real-time applications.

#### 3.5.2 Experimental Measurement

An overview of the experimental system is depicted in Fig. 3.5.4. The experimental system consists of a Xilinx ML605 FPGA board and a host computer which are directly connected by a dedicated Gigabit Ethernet cable (indicated as "GbE" in Fig. 3.5.4). To simulate a disordered input stream, we implement a synthetic data generator to produce an input stream with bounded disorder. The schema of the input stream is defined as follows: *Trades* =  $\langle Symbol : char[4], Price : int, Volume : int, Time : int \rangle$ . The *Symbol* attribute contains either a constant string "UBSN" or other randomly generated strings of 4 characters (4 bytes). The *Price* and *Volume* attributes contain uniformly distributed random integers from the interval 1–100 and 1–1000, respectively. The *Time* attribute contains sequential numbers starting from 0 with an incremental interval of 1. The data generator on the host computer first generates 147,200 input tuples in non-decreasing order with respect to their *Time* attribute. After that, the positions of the tuples are randomized in such a way that no tuples are to be late or out-of-order more than 60 seconds (*i.e.*, a predefined *SLACK* value) in the stream.

We measured the number of clock cycles elapsed from when the first tuple arrived at the UDP Rx module until the last result was transferred from the UDP Tx module. For each configuration (*i.e.*,  $RANGE = 10 \sim 60$  minutes), we calculated the maximum throughput achieved by the experimental system, using the measured values. It should be noted that all results generated by the query circuit have been verified by the host computer. This has been confirmed by comparing expected results with those sent from the UDP Tx module. In our experiments, we obtained exactly the same results as those

expected. This means that the proposed implementation can properly handle out-of-order tuples.