| Contents                                    | 1     |

|---------------------------------------------|-------|

| 第1章 はじめに                                    | 3     |

| 1.1 LED の歴史と現状                              | 3     |

| 1.2 研究背景                                    | 4     |

| 1.3 ITO と GaAs のオーミック性接触                    | 5     |

| 1.4 研究目的                                    | 11    |

| 第 2 章 スズ添加酸化インジウムの紹介(Indium-Tin-Oxide: ITO) | 13    |

| 2.1 ITO の特性                                 | 13    |

| 2.1.1 酸化インジウムの結晶構造                          | 13    |

| 2.1.2 ITO の薄膜の電気的特性                         | 14    |

| 2.1.3 ITO の光学的特性                            | 18    |

| 2.1.4 ITO の透明性                              | 20    |

| 2.2 ITO の成膜方法                               | 21    |

| 2.2.1 スパッタリング法                              | 22    |

| 2.2.2 スプレー法                                 | 23    |

| 第3章 実験方法                                    | 25    |

| 3.1 作製方法及び評価方法                              | 25    |

| 3.1.1 ITO 特性測定用試料の作製方法                      | 25    |

| 3.1.2 ITO/GaAs の I-V 特性用試料の作製方法             | 27    |

| 3.1.3 LED の立ち上がり電圧用試料の作製及び評価                | 29    |

| 第4章 実験結果                                    | 31    |

| 4.1 スプレー法とスパッタ法による ITO の特性比較                | 31    |

| 4.1.1 ITO 薄膜の電気特性                           | 31    |

| 4.1.2 ITO 薄膜の光学特性                           | 33    |

| 4.2 スプレー法とスパッタ法による ITO/GaAs の I-V 特性及びコンタク  | ト抵抗の比 |

| 較                                           | 35    |

| 4.3 スプレー法による ITO/LED の立ち上がり電圧 $V_F$         | 45    |

| 5章 結論                                       |       |

| 謝辞                                          | 49    |

| 参考文献                                        | 50    |

| 付録                                          | 52    |

| 付録A    | 四探針法                                         | 52 |

|--------|----------------------------------------------|----|

| 付録B    | 電子ビーム蒸着                                      | 53 |

| 付録 C   | RF マグネトロンスパッタリング法                            | 54 |

| 付録 D   | <b>CTLM</b> 法を用いた <b>I-V</b> 特性、及びコンタクト抵抗の測定 | 57 |

| D.1 TL | M 法                                          | 58 |

| D.2 CT | LM 法                                         | 60 |

# 第1章 はじめに

## 1.1 LED の歴史と現状

LED は半導体の p-n 接合に順方向電流を流すと発光する素子であり、光の閉じ込めと電流狭窄を行うため、通常はダブルヘテロ (DH) 接合、および量子井戸 (QW) 構造を用い

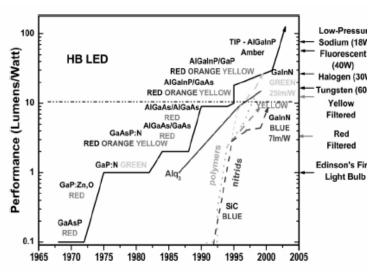

る。可視光 LED の開発の歴史はまだ新しく、GaAsPで1962年、赤色 LED を商品化したのが始まりであると考えられている。ほとんどの可視光 LED において、約10年ごとに約1桁の割合で発光効率が向上している(図1.1 参照)。2000年にはInGaN 混晶を活性層とした量子井戸構造で高度10cd以上の青色、緑色 LED が開発された。さらに、AlInGaPアンバーLED で外部量子効率50%をこえるものが開発された。青色および、近紫外 LED も、この値に近づくものと考えられている。

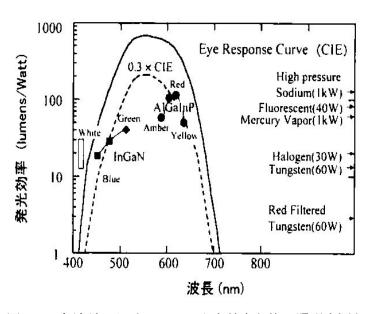

図1.2は、各種LEDの発光効率を波長ごとに整理し、他の照明光源の発光効率と比較したものである。AlInGaP、InGaN系のLEDではすでに30Wのハロゲン電球の発光効率を上回り、40Wの蛍光灯のそれを超えている。

図 1.1 各種 LED の発光効率の推移

図 1.2 各波長における LED の発光効率と他の照明光源との比較 実線は人間の視感感度を示す CIE 曲線、点線はその 3 0 %の値

#### 1.2 研究背景

透明導電膜とは可視光(波長領域 380nm~780nm)にて透過率が高く、なおかつ導電率を併せ持つ薄膜のことである。透明導電膜材料には本研究で扱う酸化インジウムスズ(ITO)や酸化亜鉛、酸化スズなどが有名であるが、そのなかでも ITO は他の材料と比べて、低抵抗性、高透過率性の点で最も優れており、さまざまな光デバイス用の透明電極として現在もっとも幅広く用いられている。

| 種類       | 薄膜材料                                                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------|

| 金属薄膜     | Au、Ag、Pt、Cu、Rh、Pd、Al、Cr                                                                                   |

| 酸化物半導体薄膜 | $In_2O_3$ , $SnO_2$ , $ZnO$ , $CdO$ , $TiO_2$ , $CdIn_2O_4$                                               |

|          | Cd <sub>2</sub> SnO <sub>4</sub> 、Zn <sub>2</sub> SnO <sub>4</sub> 、In <sub>2</sub> O <sub>3</sub> -ZnO 系 |

| スピネル形化合物 | MgInO <sub>4</sub> , CaGaO <sub>4</sub>                                                                   |

| 導電性窒化物   | TiN、ZrN、HfN                                                                                               |

| 導電性ホウ化物  | LaB <sub>6</sub>                                                                                          |

| その他      | 導電性高分子                                                                                                    |

表 1.1 代表的な透明導電膜材料

不純物の入っていない  $In_2O_3$  が 10s 程度の導電性を示すことをはじめて明らかにしたのは 1954 年の G. Rupprecht の論文であった。金属インジウムを石英ガラス基板に真空蒸着でつけ、これを空気中 700 度~1000 度で短時間熱処理して透明化したもので、膜厚は  $600\sim2500$  Åであった。この方法で  $In_2O_3$  膜ができたのは当時の真空装置が拡散ポンプで排気する低真空装置のお陰であったということができる。インジウム膜がわずかに酸化していたために石英ガラス上に連続膜を形成でき、このためにこれを後熱処理で透明化することによりその導電性を測定することができた。

1970 年を過ぎると主として学術講演界にて液晶が登場し始める。液晶の特徴としては電界を印加することにより液晶分子の配列方向が変わって可逆的な光シャッターとなることがあげられる。そのため液晶に電圧を印加するための透明導電膜にも関心が集まり、結果として1971年のJ. L. Vossen、あるいは1972年のD. B. FraserとH. D. Cookの直流スパッタ法によるITO膜の発表にもつながっていく。

スパッタ法による ITO 膜の作製はその後2~3年にてマグネトロンスパッタによって高

速成膜が可能になったこと、膜厚分布、導電性分布において高い均一性が得られやすいこと、 プロセスの安定性が高いことなど好ましい要因が相まってスパッタ ITO 膜として次第に普 及していくこととなる。

現在では真空装置の性能向上やスパッタ装置の改良などによりマグネトロンスパッタ法によって  $1 \times 10^{-4} \Omega \cdot \text{cm}$  程度の低抵抗の ITO 薄膜を容易に作製することができる。

これまで本研究室では、スパッタ法で成膜した ITO を用いた時の ITO/GaAs のオーミック特性及び固有接触抵抗の低減化、また ITO とは不純物の異なる材料、チタン添加酸化インジウム(Indium-Titanium-Oxide:ITiO)をスパッタ法で成膜した時の ITiO/p-GaAs、ITiO/n-GaAs のオーミック特性及び固有接触抵抗の低減化について研究を続けてきた。

また、本研究室の研究では、ITO や ITiO といった透明導電膜をスパッタ法により成膜し、p 型伝導 GaAs 基板上に堆積した時、as-deposit で非オーミック特性となり、 $N_2$  雰囲気中で  $700^{\circ}C20$  秒間のアニールを行った後でオーミック特性を得られるということが明らかになった。

しかし、これらの研究は透明導電膜の成膜をスパッタ法により行ってきた。スパッタ法は大面積で緻密な膜を作製できる反面、プラズマによる高いエネルギーで粒子を衝突させて膜を作製するために、成膜による基板側へのダメージや、雰囲気ガス中の  $O_2$  による基板の劣化等が懸念され、透明導電膜と基板のオーミック性接触に影響を与える問題が考えられ、n型伝導 GaAs 基板上に堆積した時、as-deposit で非オーミック特性となり、 $N_2$  雰囲気中で $700^{\circ}C20$  秒間のアニールを行った後でもオーミック特性を得られないということが明らかになった。

#### 1.3 ITO と GaAs のオーミック性接触

ITO は前述したとおり、3eV 以上のワイドバンドギャップを有し、かつ、キャリア密度が  $10^{20}cm^{-3}$  以上と高いため、フェルミ準位が伝導帯に入り込み、仕事関数  $E_{ITO}$  は約 5.2eV となり,金属に近い状態であると言える。ITO の仕事関数  $E_{ITO}$  が p-GaAs/n-GaAs の仕事関数  $E_{p}$ -GaAs/n-GaAs との比較について理論的なバンドアライメントについて説明する。

仕事関数の異なる金属と半導体を接触させると、電荷の移動が生じて両者のフェルミ準位

が同じ高さになるところで平衡状態となる。この場合、接触させる金属と半導体の仕事関数のどちらが大きいかによって、ショットキー性接触、あるいはオーミック性接触のいずれかに分かれる。オーミック接触は、整流性をなくし、半導体バルクの抵抗による直列抵抗に比べて無視できるほど小さな接触抵抗を有する金属・半導体接触と定義される。電流・電圧特性は図1.3のようにオームの法則に従う。

V

図 1.3 オーミック性の電流(I)-電圧(V)

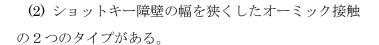

次に(2)について考えてみる。接触抵抗を低下させるためには、金属 - 半導体障壁を低くすることが必要であった。しかし、障壁の幅が 50nm 以下になると、電子やホールは障壁内のバンドギャップ(界面付近の空乏層になっているところ)を透過することが可能となる。この時の金属 - 半導体接触のバンド図を図 1.4 に示す。これは、量子力学的なトンネリング効果と理解されている。半導体中の不純物濃度を例えば、10<sup>18</sup> 個/cm<sup>-3</sup> 程度まで増加させてやれば、結果的に障壁の幅が薄くなり、電子やホールのトンネリングが可能となり、事実上オーミック接触となる。

図 1.4 障壁が狭い場合のオーミック接触

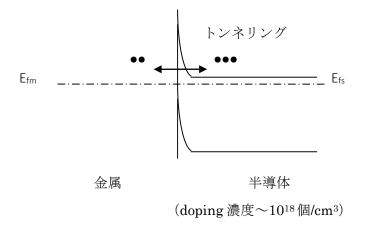

#### (i) ITO/p-GaAs の場合(φ<sub>p-GaAs</sub>=5.5eV>φ<sub>ITO</sub>=5.2eV)

ITO/p-GaAs のオーミック性接触について述べる。ITO のフェルミ準位が p-GaAs のフェルミ準位より高いので、接触により ITO から p-GaAs へ電子が移動して、p-GaAs の価電子帯の正孔が中和される。このため、p-GaAs 表面にはイオン化したアクセプタの負イオンが散在して負に帯電し、ITO 表面は電子が不足して正に帯電する。この結果として、p-GaAs表面のエネルギー帯は図に示すように下向きに湾曲し、正孔に対するショットキー障壁ができる。

拡散電位は

$$_{\rm eV_d} = \varphi_{\rm p \cdot GaAs} - \varphi_{\rm ITO}$$

(1.3.1)

で与えられ、ITO 側から見た障壁高さは  $E_{p-GaAs}-\varphi_{TO}$ となる。  $\phi_{p}$ -GaAs は真空準位から 測定した価電子帯頂上までのエネルギーである。P-GaAs 側から ITO 側への正孔の移動には 拡散障壁 eVd を越えなければならず、ITO 側から GaAs 側への正孔の移動にも  $\phi_{p-GaAs}-\phi_{p-GaAs}$  の障壁を越えなければならない。外部からの印加電圧は障壁層のみにかかるので、p-GaAs 側から見た障壁の高さを変えることになる。したがって、p-GaAs のドープ濃度が高ければ、正孔はトンネリング効果による ITO 側に移って電流がよく流れ、オーミック性接触となる。

図 1.5 ITO/p-GaAs 接触

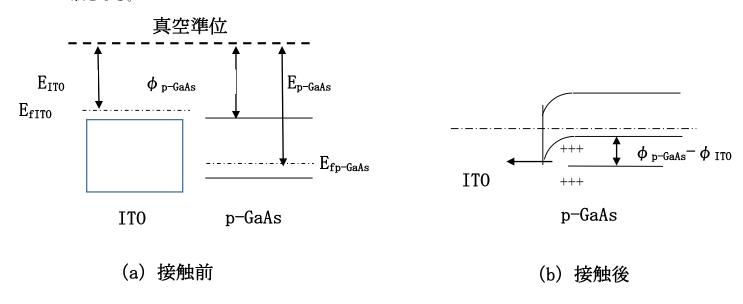

#### (ii) ITO/n-GaAs の場合(φ<sub>n-GaAs</sub>=4.5eV<φ<sub>ITO</sub>=5.2eV)

ITO/n-GaAs のオーミック性接触について述べる。ITO のフェルミ準位が n-GaAs のフェルミ準位より低いので、接触直後、フェルミ準位が異なるため電子の拡散とドリフトが起こり、これらの電流が等しくなったとき、フェルミ準位が一致し、熱平衡状態となる。図 1.6(b)から分かるように電子の移動を妨げる障壁が生じする。ITO 側から n-GaAs を見たときのエネルギー障壁 $\phi$ Bn をショットキー障壁という。この障壁のために、n-GaAs に印加電圧を加えた場合、ドープ濃度が高ければ、電子はトンネリング効果による ITO 側に移って電流がよく流れ、オーミック性接触となる。

図 1.6 ITO/n-GaAs 接触

次に、コンタクト金属について述べる。コンタクト金属とは、主として半導体とオーミック接触を得るための電極材料として用いられる金属のことである。また、他のコンタクト金属との密着性を良くするために中間層として挿入される金属もまた、こう呼ばれることがある。つまり、

- ✓ 電気的な密着性

- ✓ 物理的な密着性

の2つを目的として用いられる金属がコンタクトメタルである。コンタクト金属として使用されている金属のうち、主なものを表 1.2 に示す。Ni はコンタクト金属としてよく利用されている。特に Ga 系III-V 族の半導体においては非常に密着性が良く、例として GaAs に AuGe / Ni / Au の電極を蒸着する場合、初めに Ni を薄く( $\sim$ 50 Å程度)堆積することで密着性の高い電極を作製することができる。また、Ni は空気中の塵や埃を吸着する性質を持っており、それらの金属を初めに飛ばすことは、チャンバー内の真空度を高くすることにもつながり、前述の密着度向上に加えてもう 1 つの利点となる。

次に、固有接触抵抗について述べる。半導体のオーミック接触の性能を定量的に示す指標として金属・透明電極と半導体の接触抵抗 $[\Omega]$ や接触抵抗率 $\rho_c[\Omega\cdot cm^2]$ がある。固有接触抵抗を測定するのに用いられる方法として Transmission Line Model (TLM) 及び Circular Transmission Line Model (CTLM) が用いられている。

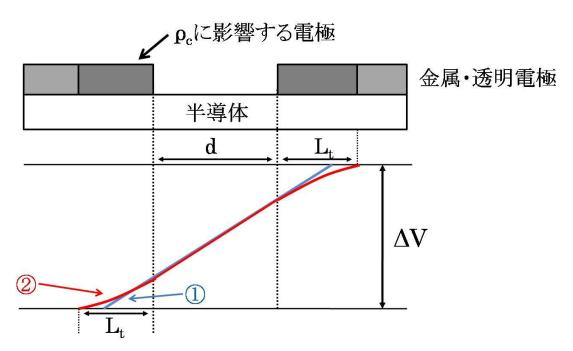

半導体上に金属もしくは透明電極を堆積し、距離 d だけ離した 2 つのコンタクト電極の I-V 測定を行う場合、図 1.7 の①の直線のような電圧降下が理想的である。しかし、実際には電極直下において②に示すような曲線となり、そして上図に示すような伝搬長  $L_t$  を定義する。電流は事実上、電極内の距離  $L_t$  の範囲で流れているとみなすことができ、この伝搬長  $L_t$  の距離だけ抵抗が電極直下に入り込み、金属・透明電極と半導体の接触抵抗に影響を与えている。

金属・透明電極と半導体との固有接触抵抗率については次式で表される。

$$\rho_c = R_c \cdot L_t^2 [\Omega \cdot cm^2] \tag{1.1}$$

デバイスに応用する場合、金属・透明電極と半導体との固有接触抵抗について一般的には 10<sup>-3</sup>以下の値が望まれる。

表 1.2 主なコンタクト金属

| 金属 | 仕事関数[eV] |

|----|----------|

| Au | 5.10     |

| Pt | 5.65     |

| Ag | 4.26     |

| Ni | 5.15     |

| Al | 4.28     |

| Pd | 5.12     |

| Ti | 4.35     |

図 1.7 伝搬長と電圧降下の関係

## 1.4 研究目的

LED では、電気を光に変換する発光素子である。低電圧で立ち上がり、小型及び長寿命のメリッドを生かし、主にディスプレイやインジケータの光源として用いられてきた。この応用範囲を開けるために、発光効率の向上が必要だ。

本研究で使われている AlGaInP 赤色系の LED では、図 1.8 に表すように GaAs 基板上にエピタキシャル成長による作られる。発光層の下に GaAs 基板がある構造では、発光層から、GaAs 基板に向かった光は GaAs に吸収されることにより、光を取り出す効率の低下が懸念される。

本研究では、図 1.9 に表すように光を GaAs 基板に吸収されないように、LED の GaAs 基板を取り除いて、代わりに ITO 透明導電膜をつけ、ITO 膜と金属光によるを反射させ、発光効率の向上を狙っている。

通常はスパッタ法により ITO 透明導電膜を成膜する場合、プラズマによる高いエネルギーの粒子を基板に衝突させるので、基板へのダメージが懸念される。また、本研究室の先輩の実験結果に基づいては、p型の GaAs 基板上にスパッタ法による ITO 透明導電膜を成膜する場合、アニールしなくでも、オーミック特性となるが、n型では、as-deposit と 700℃で20 秒間のアニールを行った時、どちらでも非オーミック特性となった。それらの原因に関しては、1.3 に説明したように、ITO の仕事関数 Erro(5.2eV)が p-GaAs の仕事関数 Ep-GaAs (5.5eV)よる小さい、n-GaAs の仕事関数 En-GaAs (4.5eV)よる大きいから、理論的は両方ともショットキー特性となり、高ドープ濃度の GaAs 基板を用いて、トンネリング効果によるオーミック接触となるが、しかし、スパッタ法により ITO 透明導電膜を成膜する場合、プラズマによる高いエネルギーの粒子を基板に衝突させるので、基板へのダメージの発生することにより、禁止帯にアクセプタ準位を差し入れ、電子トラップという欠陥が生じ、電子がアクセプタに捕まって、イオン化になって、ドーピング濃度が減り、空乏層の幅が広かり、トンネリング効果がなくなるため、オーミック特性にならないと考えられる。

こういうような問題を解決するため、本研究では新たに、スパッタ法ではなく、基板側へのダメージの少ないスプレー法による ITO の成膜を試み、ITO 特性の条件を最適化し、その後 GaAs/LED 基板上に ITO を成膜し、ITO と p-GaAs/n-GaAs 間の I-V 特性及び固有接触抵抗を調べ、片面に ITO つけたサンプルと両面に ITO つけたサンプルの立ち上がり電圧  $V_f$  を比較することを目的とした。

| ITO                |         |

|--------------------|---------|

| p- <u>GaAs</u>     | キャップ層   |

| p- <u>AlGaInP</u>  | P型クラッド層 |

| GaInP              | 発光層     |

| n-AlGaInP          | n型クラッド層 |

| n- <u>GaAs</u>     | バッファー層  |

| n- <u>GaAs</u> Sub |         |

| Metal              |         |

|                    | •       |

図 1.8

| ITO               |

|-------------------|

| p- <u>GaAs</u>    |

| p-AlGaInP         |

| GaInP             |

| n- <u>AlGaInP</u> |

| n- <u>GaAs</u>    |

| ITO               |

| Metal             |

図 1.9

# 第 2 章 スズ添加酸化インジウムの紹介(Indium-Tin-Oxide: ITO)

ここでは、一般的な ITO の電気的特性及び光学的特性と、ITO の成膜方法についてまとめた。また、金属と半導体のオーミック性接触についてもこの章で簡単にまとめた。

### 2.1 ITO の特性

## **2.1.1** 酸化インジウムの結晶構造

電気伝導性酸化物薄膜の中でもSnドープ $In_2O_3$ (ITO)薄膜は,他の材料と比較して高透過率性と高電気伝導性の双方で最も優れており,また酸溶液によるウェットエッチングによって透明電極微細パターンの形成が容易であるなどに理由により,様々な光デバイス用の透明電極として現在最も幅広く用いられている。

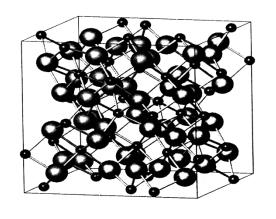

酸化インジウムは立方晶系:  $In_2O_3$  [I]と六方晶系:  $In_2O_3$  [II]の二つの異なる結晶系を持つことが知られている。これらの結晶構造に関するデータを表 2.1 に記す。

| 結晶系                                   | 格子定数(Å) | 1 ユニットセル<br>中の In <sub>2</sub> O <sub>3</sub> の数 | 密度<br>〔g/cm〕 | 結晶構造                                   |

|---------------------------------------|---------|--------------------------------------------------|--------------|----------------------------------------|

| In <sub>2</sub> O <sub>3</sub> [ I ]  | 10.117  | 16                                               | 7.12         | M <sub>2</sub> O <sub>3</sub> [I]型酸化物  |

| In <sub>2</sub> O <sub>3</sub> [ II ] | 5.487   | 6                                                | 7.31         | α -Al <sub>2</sub> O <sub>3</sub> 型酸化物 |

表 2.1 In<sub>2</sub>O<sub>3</sub>の結晶構造に関するデータ

図 2.1 In<sub>2</sub>O<sub>3</sub>[I]の結晶構造

図 2.2 蛍石の結晶構造

(小さな球が In 原子、大きな球が酸素原子)

立方晶系:  $In_2O_3$  [I]の単結晶は薄い黄色(Pale yellow)を呈している。通常の PVD, CVD などの合成プロセスで得られる  $In_2O_3$ , あるいは 10wt%程度以下の Sn をドープした ITO は,ほぼ全てこの立方晶系:  $In_2O_3$  [I]の結晶構造である。結晶化温度が約  $150\sim160^\circ$ Cであるアモルファスの  $In_2O_3$  や ITO を大気中の焼成で結晶化させた場合も同様である。

六方晶系:  $In_2O_3$  [II]は密度が  $In_2O_3$  [I]よりもわずかに大きく,高圧で安定な相であり,65kbar, $800\sim1500$   $\mathbb C$  で得られる。この結晶構造はコランダム( $corundum: \alpha -Al_2O_3$ )型で単位胞は 6 分子からなる。単結晶は無色である。通常の薄膜合成プロセスでは  $In_2O_3$  [II]を成膜するのは困難である。

## 2.1.2 ITO の薄膜の電気的特性

導電率は抵抗率の逆数であり次式であらわされる。

$$\sigma = \frac{1}{\rho} = eN\mu$$

(σ:導電率、ρ:抵抗率、e:素電荷、N:キャリア密度、μ:移動度) つまり導電率を増加させるためにはキャリア密度および移動度を増加させればよい。 <キャリア密度>

$In_2O_3$ はバンドギャップが 3.75eV のワイドバンドギャップ半導体であり、完全に化学量論比を満たす単結晶は絶対零度では絶縁体的に振舞う。しかし結晶構造が乱れない程度のわず

かな還元で化学量論比からわずかにずれることにより室温にて  $10^{18}\sim10^{19}$ cm $^{\cdot3}$ 程度のキャリア密度を持つ。これは近接した  $\ln$  原子の 5s 軌道が酸素空孔の位置で重なることにより、酸素空孔が 2 個の電子を放出するドナー準位を形成するからであると報告されている。

$$O \to V + \frac{1}{2}O_2(g) \tag{2.1}$$

$$V \rightarrow V^{2+} + 2e^{-} \tag{2.2}$$

(O:酸素、V:酸素空孔)

このように Sn ドープされていない In<sub>2</sub>O<sub>3</sub> 薄膜の電気伝導度は酸素の不足によって生じる 欠陥に大きく依存している。このため電気伝導度は成膜中のガス組成(主にその中の酸素分 圧)、ガスの反応性、および成膜後の加熱条件などに大きく影響をうける。

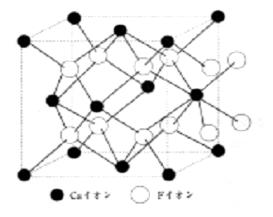

$In_2O_3$  は  $5\sim10\%$ の Sn をドープすることにより  $10^{20}\sim10^{21}$  のキャリア密度を安定して得ることができる。これは結晶中の In 原子(原子価:3 価)を Sn 原子(原子価:4 価)が置換することにより Sn は電子を一つ放出し、ドナー順位を形成することになる。しかし Sn をドープすればするほどキャリア密度は上昇するというわけではない。 Kostlin、 Manifacier らの実験によると Sn 濃度 [at%] が  $0\sim4\%$ までは Sn 原子 1 個が 1 個の原子を放出すると仮定した直線にほぼ従ってキャリア密度は上昇する(図 2.3 参照)。しかし Sn 濃度が  $5\sim10\%$ まで増加するとキャリア密度はその直線よりも小さな値を示し、10%程度でキャリア密度は飽和し、それよりも Sn 濃度が増えるとキャリア密度は逆に減少してしまう。これは Sn 濃度の増加に伴い、キャリアを一つ放出している  $In^{3+}$ サイトの  $Sn^{4+}$ 同士の距離が縮まることでクーロン反発が強まり  $In_2O_3$  の格子定数を引き伸ばしているためと考えられる。

図 2.3 ITO 膜の Sn 濃度とキャリア密度の関係

#### <移動度>

キャリアの移動度を決定する縮退半導体中の散乱機構として、一般的に次の5つの要因が考えられる。

- ① 中性不純物散乱

- ② イオン化不純物散乱

- ③ 格子振動(音響フォノン、極性光学フォノン)による散乱

- ④ 転位による散乱

- ⑤ 結晶粒界による散乱

ITO の移動度を決定する主な要因としては中性不純物散乱、イオン化不純物散乱がある。 イオン化不純物の散乱中心はキャリアを放出する酸素欠陥や置換した Sn 原子である。そ のためキャリア密度を高めるとそれによってイオン化不純物散乱は増える。しかし Dingle の理論式によるとキャリア密度の増加により散乱は増えるもの、そのときの移動度の減少は おおよそキャリア密度の 1/3 乗に反比例する程度なので他の散乱機構を問題としないなら、 キャリア密度の上昇にしたがって導電率はキャリア密度の増加の 2/3 乗に比例して増加する。 中性不純物散乱はキャリア放出に寄与していない Sn 原子、SnO<sub>2</sub>のコンプレックスなどが 原因であると考えられている。これはキャリア密度の増減に依存しないため、比抵抗の減少 のためにはこの散乱中心をできるだけ減らす必要がある。

ITO 薄膜の抵抗率を低くするためには、キャリア密度を最大にすると同時にこれらの散乱要因を最小にし、キャリアの移動度を最大にする必要がある。

これらの散乱機構はそれぞれ異なる温度依存性を持つことが知られている。そこでITO薄膜のホール効果の低温測定を行うことにより、実際に散乱に最も寄与している要因を 推定することが可能となる。その結果、抵抗率が  $10^{-4}\Omega \cdot \mathrm{cm}$  台の ITO に関しては、低温における移動度の温度依存性が殆どないことが確認された。従って、③4の寄与の可能性は低いと見られる。また、5に関しても相関が見られないことが実験的に確認されている結果として、ITO の移動度を決める散乱要因としては2を考えればよい。

ドナー原子やアクセプタ原子は不純物であり、キャリアから見れば散乱の原因である。不 純物原子がイオン化していればイオン化不純物散乱、そうでなければ中性不純物散乱となる。 中性不純物散乱による移動度の式は次のようになる。

$$\mu_N = \frac{m^* e^3}{20\varepsilon_0 \varepsilon_r \hbar^3 n_N} \tag{2.3}$$

ここで、 $\epsilon_r$ : 低周波における比誘電率(ITO は 9)、 $n_N$ : 中性散乱中心濃度、 $m^*$ : ITO の有効質量である。上式より、中性散乱濃度が増加すると移動度が減少することが分かる。イオン化不純物散乱によって決定される移動度は、Dingle の理論によりキャリア密度と関連付けることができる。

$$\mu_I = \frac{24\pi^3 (\varepsilon_0 \varepsilon_r)^2 \hbar^3 n}{e^3 m^* g(x) Z^2 n_I}$$

(2.4)

ここでg(x)およびxは

$$g(x) = \ln\left(1 + \frac{4}{x}\right) - \left(1 + \frac{x}{4}\right)$$

$$x = \frac{4e^2 m^*}{4\pi\varepsilon_0 \varepsilon_r \hbar^2 (3\pi^5)^{1/3} n^{1/3}}$$

(2.5)

となる。ここで $\mathbf{Z}$ および $\mathbf{n}_{\mathrm{I}}$ はイオン化散乱中心の電荷および濃度である。この式によると、キャリア密度の増加により散乱は増えるものの、そのときの移動度の減少はおおよそキャリア密度の 1/3 乗に反比例する程度なので、抵抗率は単調に減少する。これら 2 つの散乱要因

による移動度は、全体として次式のようになる。

$$\frac{1}{\mu} = \frac{1}{\mu_N} + \frac{1}{\mu_I} \tag{2.7}$$

ここで $\mu$ は ITO の移動度、 $\mu$ N は中性散乱中心のみによる移動度、 $\mu$ I はイオン化散乱中心のみによる移動度である。ITO の移動度の限界値は約 90cm<sup>2</sup>/Vs と言われている。

#### <抵抗率>

一般的に抵抗率はキャリア濃度、移動度と電荷の積によるものである。

$$\rho = en\mu \tag{2.8}$$

現在、標準的な低抵抗率 ITO 薄膜の電気特性は抵抗率  $1.5\sim2.0\times10^{-4}\Omega\cdot\text{cm}$ 、キャリア密度  $6\sim9\times10^{20}\text{cm}^{-3}$ 、移動度  $30\sim40\text{cm}^2/\text{V}\cdot\text{s}$  であるが、RF(または DC)マグネトロンスパッタリング法により、 $1.0\times10^{-4}\Omega\cdot\text{cm}$ (基板温度  $300\sim400^\circ$ C)、 $1.5\times10^{-4}\Omega\cdot\text{cm}$ (基板温度  $100\sim200^\circ$ C)の ITO 膜の量産レベルでの成膜方法が確立されている。

# 2.1.3 ITO の光学的特性

ITO 薄膜は可視光領域において「透明」であるが、「透明である」ということは光を吸収・反射しないということである。固体物理学では光と関係するのは電子の振る舞いである。 どんな条件ならば光を吸収・反射しないのか、それぞれのメカニズムについて詳述する。

#### <光の吸収>

物質は、そのバンド構造により絶縁体・半導体・金属に大別されるが、このうち絶縁体と 半導体はエネルギーギャップ幅が異なるというだけで、本質的には同じである。エネルギー ギャップのある物質に対して、そのギャップ幅より小さいエネルギーの光を照射しても電子 のバンド間遷移は起こらず、光は吸収されない。光の波長とエネルギーの関係式は

$$E = hv = \frac{hc}{\lambda}$$

(h:プランク定数、c:光速) (2.9)

であるので、紫外光の波長を約380nmとすれば、

$$\frac{6.62 \times 10^{-34} \times 3.0 \times 10^{8}}{380 \times 10^{-9}} = 5.52 \times 10^{-19} [J] \cong 3.4 [eV]$$

(2.10)

つまり、エネルギーギャップがおよそ 3.4eV より大きければ、可視光領域より長波長の光は吸収されない。遷移金属を含む物質は例外として、物質中の化学結合のイオン性が大きいほど、一般にエネルギーギャップは大きい。酸化物はイオン性でギャップが大きく、無色透明という条件を元来備え持っており、化学的に安定な物質である。 $In_2O_3$  のバンドギャップは約 3.75eV であり、可視光領域では透明であると言える。

#### <光の反射>

金属はエネルギーギャップが無いので光を吸収しないが、反射して特有の光沢を示す。金属の電子状態は伝導帯に多数存在する自由電子である。この自由電子が光を反射する 要因であると言われている。半導体における自由電子に相当するもの、つまりキャリア 密度が光の反射と関わっているわけである。表 2.2 は代表的な金属と透明導電性材料の代表である ITO の電気的性質である。

物質  $\lambda_{\rm p}(\rm nm)$ n И  $(\times 10^{-6} \Omega \cdot cm)$ [プラズマ周波数]  $(\times 10^{22} \text{cm}^{-3})$  $(c m<sup>2</sup>/V \cdot s)$ Li 9.34 3.67 18.2 1741.61 6.956130 Ag ITO 100 0.1 100 1000

表 2.2 代表的な金属と ITO の電気的性質

ITO に関する値は縮退半導体化した状態 (キャリア密度が十分高く、フェルミ準位が伝導帯中に入っている状態) でのおよその値である。ITO は典型的な金属に比較して抵抗率が 1 ~2 桁大きく、その原因はキャリア密度が低いためであることがわかる。典型的な金属は  $10^{22}$ cm<sup>-3</sup>以上のキャリア密度を持っており、特有の光沢を示す。金属中のキャリアは一種のプラズマ状態にあり、光と強く相互作用する。

反射される光の波長にはプラズマ周波数(プラズマ振動の周波数)で決められる閾値があり、 そのエネルギーより低エネルギーの光は反射される。プラズマ周波数 $\omega_p$ は式(2.11)で定義され、キャリア密度 n の関数になっている。

$$\omega_p^2 = \frac{ne^2}{\varepsilon m^*} \tag{2.11}$$

ここで、e:キャリアの電荷、 $\epsilon$ :誘電率、m\*:有効質量である。

表 2.2 で示した  $\lambda_p$  は有効質量を電子の質量、誘電率を真空の誘電率として求めた  $\omega_p$  を波長に変換したものである。典型的な金属ではプラズマ周波数は紫外領域に存在し、それよりエネルギーの低い可視光は全て反射されてしまうことがわかる。

一方、ITO はプラズマ周波数が近赤外線領域に存在し、赤外線は反射されてしまうが、可 視光は反射されない。従って可視光領域では透明であると言える。また、このプラズマ反射 を利用して、高キャリア密度の透明導電材料は赤外線反射材としても応用されている。

#### 2.1.4 ITO の透明性

ITO に対して可視光は価電子帯の電子も励起できず、伝導帯底部のキャリアによっても反射されない光である。仮に人間の目が赤外領域のみの光を検知するならば、Li や Ag と ITO を区別できず、いずれも金属光沢を示すだろう。ITO が透明電極として使われているのは全く人間の都合であることがわかる。

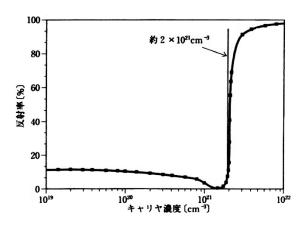

図 2.4 800nm における反射率のキャリア密度依存性<sup>4)</sup>

無色透明性を保ちつつ抵抗率を低減させるために、どのような程度までキャリア密度を多くできるかは重大な問題である。図 2.4 は典型的な透明電極材料の誘電率などを用いて計算した波長 800nm での反射率のキャリア密度依存性である。反射率はキャリア密度が約  $2\times 10^{21}$ cm<sup>-3</sup> から急激に大きくなり、長波長側の可視光を反射し始める。したがって、無色透明性を保つためには n は約  $2\times 10^{21}$ cm<sup>-3</sup> 以下に抑えなければならないことがわかる。

また、抵抗率とキャリア密度の関係において、文献により低抵抗と報告された値と理論を

比較したところ,どの値も理論と同様の挙動を示しており,イオン化不純物による散乱機構が電気抵抗率を支配していることを示唆した。この時の理論値は電気抵抗率の下限を示しており移動度の上限は $90\text{cm}^2/\text{V}\cdot\text{s}$ になると考えられ,先ほどのキャリア密度の上限値とから,透明度電体の抵抗率の加減は $4\times10^{-5}\Omega\cdot\text{cm}$ と見積もられている。

#### 2.2 ITO の成膜方法

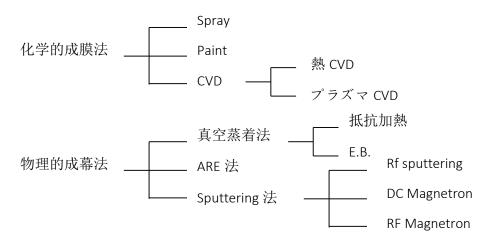

図 2.5 に示すように、ITO 膜の作製方法は spray 法(スプレー法)、paint 法(塗布法)、CVD(chemical vapor deposition)法などの化学的作製法と真空蒸着、スパッタ法などの物理的作製法に分けることができる。化学的作製法は,塩化物の加水分解や有機化合物の熱分解反応により透明導電膜を形成する方法である。工程が簡単で装置が安いというメリットはある。しかし、通常  $400^{\circ}$ 公以上の反応温度を必要とするため低温基板への膜形成ができないこと、組成の微細な制御による酸素欠損ドナーの最適化ができないため低抵抗膜を得にくいこと、有害ガスを発生することなどの問題がある。

物理的作製法のうち真空蒸着法は、真空中で金属または酸化物の原料を抵抗加熱あるいは電子ビームで加熱して基板上に薄膜を形成する方法である。蒸着法により ITO 膜を形成する場合は、通常 5wt%前後の  $SnO_2$  を含んだ  $In_2O_3$ : Sn 焼結体ペレットを蒸発材料として用いて、電子ビーム加熱により蒸発させ、膜形成を行う。この際、適量の酸素ガスを導入することにより酸素欠損ドナーの最適化を行う。

スパッタ法は Ar ガスを直流 (DC) または高周波 (RF) 放電によりイオン化し、金属または酸化物のターゲットに衝突させ飛び出したターゲット材料を基板上に析出させる方法である。とくに直交磁界を利用したマグネトロンスパッタ法は、高速成膜が可能であるため、広く用いられている。

以上のように ITO 膜には様々な成幕方法が試みられている。この章ではスパッタリング 法とスプレー方法を紹介し、検討することを目的としている。

図 2.5 各種 ITO 成膜法

#### 2.2.1 スパッタリング法

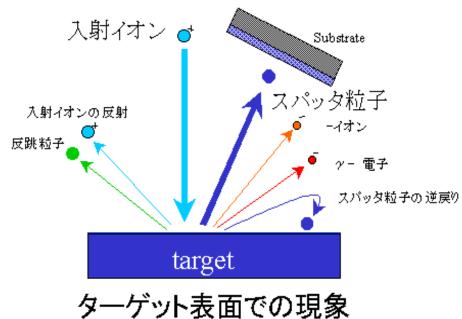

固体の表面に高エネルギーの粒子を衝突させるとその固体の表面の原子・分子がそれらの 高エネルギー粒子と運動量を交換して表面から外にはじき出される。この現象をスパッタリ ング (sputtering) 現象と呼んでいる。

実際のスパッタリング装置では加速されたイオン (ほとんどの場合 Ar) を高エネルギー 粒子としてターゲット表面に衝突させる。すると下のような現象が起こり、基板にターゲッ トの原子、分子が堆積され、膜が形成される。

スパッタ法は、透明導電膜を作製する方法として現在最もポピュラーと言われている。真空中で放電によりプラズマを発生させ、そのプラズマ中の陽イオンが負電極のターゲットに加速されて表面を衝撃し、衝撃によりターゲット物質が飛び出す。飛び出したターゲット物質を基板上に堆積させ薄膜を形成する。スパッタ法の中でもマグネトロンスパッタ法は、ターゲットの背後に配置した磁石の発する磁場により、ターゲット表面にプラズマを高密度に拘束し、高速成膜を可能にしているため、工業的な量産ラインで用いられる。

スパッタ法の利点は、大面積の基板上に均一な暑さの薄膜を作製するのに有利であること、 スパッタ粒子は高いエネルギーを保ち基板に入射するために基板への膜の付着力が強く、硬 く緻密な膜になることなどが挙げられる。

図 2.6 スパッタリングによるターゲット表面での現象

スパッタ法の欠点は、プラズマによる高いエネルギーの粒子を基板に衝突させるので、基 板へのダメージが懸念される点やコストが大きい点である。

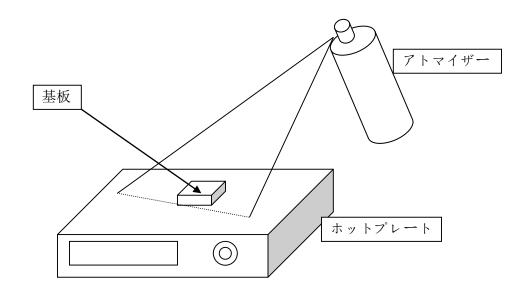

## 2.2.2 スプレー法

スプレー法とは、噴霧熱分解法(Spray Pyrolysis)あるいはスプレーCVD 法とも呼ばれる。この製法は、ITO 薄膜の原料となる塩化物(InCl<sub>3</sub>、SnCl<sub>2</sub>、SnCl<sub>4</sub>など)をアルコールなどの溶媒で溶解希釈した溶液を、噴霧器を用いて加熱された基板(ガラス,GaAs など)に噴霧して ITO 薄膜を作製する。

従来、スプレー法は、十分に研究されなかったが、その製法の創意工夫や物理特性の解明・制御手法の確立によって、以下の長所を具現化した高性能で大面積の ITO 薄膜の製造が大いに期待される。

①スプレー法による工業的製造装置は、DC スパッタリング装置( $1\sim2$ 億円)に比べて、簡素(低設備費、 $\sim0.3$ 億円)で、大面積 ITO 薄膜を大気中で製造できる量産性に富む製法である。

②スプレー法で作製した ITO 薄膜は、DC スパッタリング膜より高純度であり、Sn 低濃度 ITO 薄膜の製造に極めて有利である。

この理由は、スプレー溶液は高純度薬品から加工無しで調製できるので、不純物混入の少

ない良質の ITO 薄膜が作製できる。DC スパッタリング法では、ITO 薄膜の母材となるターゲット材料は、酸化インジウムと酸化錫粉末を熱焼結法で作製する。この熱焼結過程でターゲット中に重金属不純物(Fe、Cu など)が混入し低純度のターゲットとなり、この結果、高性能 ITO 薄膜が得られない。

#### 第3章 実験方法

## 3.1 作製方法及び評価方法

今回の実験では、測定の目的に応じて、基板及びサンプル構造を大きく分けて 3 種類で使い分けた。ITO 自体の膜の電気特性と光学特性を調べる時は、基板が絶縁性でありかつ透明である必要があるため、石英基板を用いた。一方、ITO/GaAs 間のオーミック性接触及び固有接触抵抗を求める時には GaAs 基板を用いた。そして、LED の立ち上がり電圧  $V_F$  を測定するために、AlGaInP の LED を用いた。

ITO 膜の電気的特性については、4 探針法により抵抗率の測定を行った。ITO 膜の光学的 特性については、UV スペクトルメーターを用いて透過率測定を行った。

ITO/GaAs の I-V 特性については、CTLM パターンで 2 端子法を用いて行い、得られた I-V 特性から固有接触抵抗率(コンタクト抵抗率)の算出をした。

LED の立ち上がり電圧  $V_F$ については、パルス電源を用いて、2 端子法で測定を行った。 Pulse width が 1ms、pulse time が 100ms、delay が 0.5ms だ。また、duty が 1 %だから、 温度が上がらない事が分かった。

## 3.1.1 ITO 特性測定用試料の作製方法

まず、ITO 自体の膜の電気特性と光学特性を測定するための試料の作製方法について記す。 石英基板基板上の塵や油分などの不純物を除去するために、アセトン、エタノール、5分、 純水3回30秒の順で手攪拌し、窒素ガンにより水分を除去した。

高純度化学 (株) 製の塩化インジウム  $InCl_3(99.99\%) \cdot 4H_2O$  と塩化スズ  $SnCl_2 \cdot 2H_2O(99.9\%)$ をエタノール中に濃度 0.1 mol/uになるように溶解し、マグネチックスタラーで 10 分間攪拌した。今回の実験では、Sn 濃度を 0%、5%、10%となるように溶液を調製した。溶液の条件は以下の通りである。

次に、調製した溶液を、ダイソー(株)製の化粧品用アトマイザーに入れた。アトマイザーは、溶液と反応を起こさないためにも、ガスを使用しないプッシュ式のスプレーボトルを使用した。

次に、ホットプレート上に基板を置き、基板が十分に加熱されるまで待ち、サーモペッターでホットプレートの設定温度と実際の基板温度が異なっていないか確認した。

図 3.1 のように、ホットプレート上に置かれた基板に、アトマイザーを用いて基板から

$10cm \sim 15cm$  程度の距離から 5 秒毎に 100 回吹き付けた。基板上への溶液の噴霧は、断続的に行う。すなわち、噴霧、休止、噴霧、休止と断続的に行った。 1 回の吹きつけに 5 秒間隔を空けるのは、溶液により冷えた基板の温度を回復させるためである。また、スプレー 1 回につき、形成される平均膜厚は  $1\sim 2nm$  とされている。

今回の実験では、基板温度を 250  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  も でアニールを行った。

図 3.1 スプレー法の成膜概略図

噴霧装置と基板との距離は、10~70cm の範囲にあることが好ましい。距離が 10cm 以上であると、数 mm 未満の微小サイズ基板への ITO 薄膜作製が可能に成る、という利点がある。距離が 70cm 以下であると、均一な膜厚を持つ大面積の ITO 薄膜作製が可能に成る、という利点がある。

1回の噴霧時間は、0.5~2.0 秒の範囲にあることが好ましい。噴霧時間が 0.5 秒以上であると、その噴霧時間の増加とともに、所望の膜厚をもつ ITO 薄膜作製に対して、溶液の噴霧回数を減らすことができる、という利点がある。噴霧時間が 2.0 秒以下であると、その噴霧時間の減少につれて、1回の噴霧量が徐々に減少する。この結果、溶液中材料分子の基板への付着・堆積量が減少し、基板からの材料分子の吸熱による基板温度低下を軽減できる、という利点がある。

休止時間は、3~10秒の範囲にあることが好ましい。休止時間が3秒以上であると、その

休止時間の増加とともに、基板への溶液噴霧による基板温度低下から規定の基板温度への復帰が確実に行われる、という利点がある。休止時間が 10 秒以下であると、その休止時間の減少とともに、基板表面近傍に浮遊する微細塵などを薄膜内に取り込む確率が減少し、この結果、高純度 ITO 薄膜作製が実現する、という利点がある。

基板上に形成した ITO 薄膜は、アニールすることができる。アニールすると、ITO 薄膜の結晶性が向上し、その電気特性と光学特性は、アニール無しの成膜したままの状態 (as deposited 状態) に比べて改善されるという利点がある。

アニール温度は、250~800℃の範囲にあることが好ましい。アニール温度が250℃以上であると、短いアニール時間の下で、確実にアニール効果が得られる、という利点がある。アニール温度が800℃以下であると、ITO 薄膜内に取り込まれる加熱装置表面などからの不要な不純物混入を抑制できる、という利点がある。

#### 3.1.2 ITO/GaAs の I-V 特性用試料の作製方法

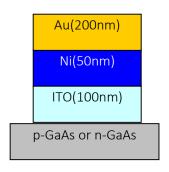

次に、ITO/GaAs の I-V 特性及び固有接触抵抗を測定するための試料作製方法について記す。作製するサンプル構造の概略図を図 3.2 に示す。

図 3.2 I-V 測定用試料構造図

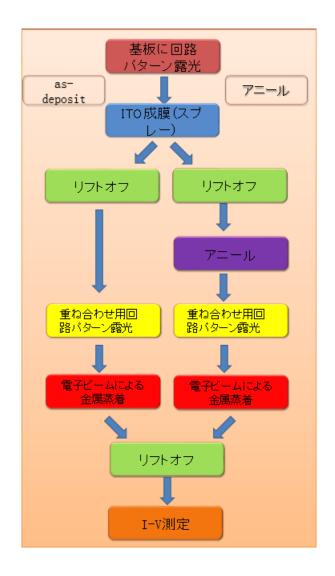

また、全体の工程の簡単な流れを示すと図3.3のようになる。

図 3.3 I-V 測定用試料作製手順

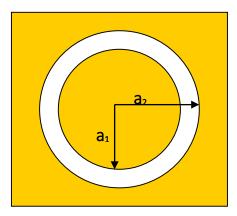

GaAs 基板上に I-V 測定及び固有接触抵抗測定のための図 3.4 のような回路パターン (Circular Transmition Line Model: CTLM) をフォトリソグラフィーにより露光した。

図 3.4 CTLM 回路パターン

ギャップ幅 (円環の白い部分の幅) は左から、 $75\,\mu$  m、 $100\,\mu$  m、 $125\,\mu$  m、 $150\,\mu$  m、 $175\,\mu$  m、 $200\,\mu$  m である。

その後、ITOをスプレー法で堆積した。ITO 成膜後、不要部分を取り除くために一度リフトオフをした。ITO のアニール処理を行う場合はリフトオフ後に、アニールを行った。その後、ITO 上に金属電極をつけるためにもう一度フォトリソグラフィーを行った。

次に、電子ビーム蒸着法により、ITO上にNi(50nm)、Au(200nm)の順に金属電極を堆積し、不要な金属部分を取り除くためにリフトオフを行った。

## 3.1.3 LED の立ち上がり電圧用試料の作製及び評価

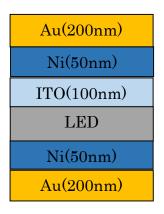

次に、LED の立ち上がり電圧  $V_F$ 特性を比較するための試料作製方法について記す。作製するサンプル構造の概略図を図 3.5 に示す。

ITO を片面につけた場は、LED の基盤上にITO をスプレー法で堆積した。ITO 成膜後、ITO 薄膜の結晶性が向上し、薄膜を固めるため、 $N_2$  の雰囲気中  $700^{\circ}$ C、20 秒間のアニール処理を行った。その次に、電子ビーム蒸着法により、ITO 上に Ni(50nm)、Au(200nm)の順に金属電極を堆積した。

図 3.5 ITO を片面につけたサンプル

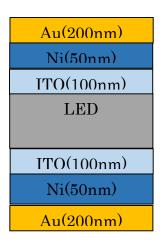

ITO を両面につけた場は、 LED 基盤の上に ITO をスプレー法で堆積した。300<sup> $\circ$ </sup>Cのホットプレート上に n 型に ITO をつけるために、 $N_2$ の雰囲気中 700<sup> $\circ$ </sup>C、20 秒間のアニール処

理を行った。その次に、同じの手順でも一度 ITO をつけ、 $N_2$  の雰囲気中 700  $^{\circ}$   $^{\circ}$

図 3.6 ITO を両面につけたサンプル

# 第4章 実験結果

# 4.1 スプレー法とスパッタ法による ITO の特性比較

ここでは、これまで本研室の先輩が ITO をスパッタ法で成膜した場合と自分がスプレー 法で成膜した場合について、ITO 薄膜の電気的特性と光学的特性について比較した。

# 4.1.1 ITO 薄膜の電気特性

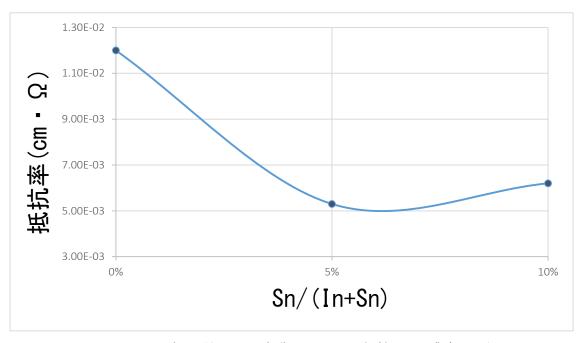

スプレー法で成膜した ITO の抵抗と Sn 濃度の関係について図 4.1 に示す。

図 4.1 スプレー法により成膜した ITO の抵抗と Sn 濃度の関係

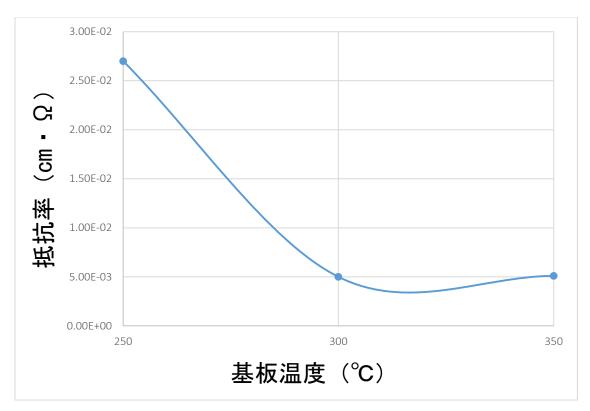

Sn 濃度 5%として、スプレー法で成膜した ITO の抵抗率と基板温度を 250  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  350  $^{\circ}$   $^{\circ}$  と変化させた時の関係を図 4.2 に示す。

図 4.2 スプレー法により成膜した ITO の抵抗率と基板温度の関係 (Sn 濃度 5%)

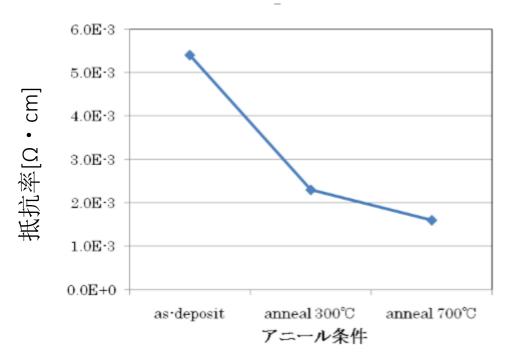

Sn 濃度 5%、基板温度を 300 $^{\circ}$ として、スプレー法で成膜した ITO をそれぞれ 300 $^{\circ}$ C、700 $^{\circ}$ Cで 20 秒間アニールした時の抵抗率の関係を図 4.3 に示す。

図 4.3 スプレー法により成膜した ITO の抵抗率とアニール条件の関係

表 4.1 に、ITO をスパッタ法で成膜した場合と、スプレー法で成膜した場合の抵抗率の関係について示す。

表 4.1 スパッタ法で成膜した ITO とスプレー法で成膜した ITO の抵抗率の比較

|       | as-deposit $\times 10^{-3} [\Omega \cdot \text{cm}]$ | anneal(700°C) $\times 10^{-3}[\Omega \cdot \text{cm}]$ |

|-------|------------------------------------------------------|--------------------------------------------------------|

| スプレー法 | 5.0                                                  | 1.6                                                    |

| スパッタ法 | 4.6                                                  | 0.65                                                   |

図 4.1 より、今回の実験範囲内では、Sn 濃度 5% の時が最も抵抗率が低く、 $5.4\times10^{-3}$  [ $\Omega$ ・cm] となった。図 4.2 より、基板温度 300 の時が最も抵抗率が低く、 $5.0\times10^{-3}$  [ $\Omega$ ・cm] となった。図 4.3 より、700 で 20 秒間アニールを行った時、最も低い抵抗率  $1.6\times10^{-3}$  [ $\Omega$ ・cm] を示した。

以上より、GaAs 基板上にスプレー法で ITO を成膜する時は、Sn 濃度 5%、基板温度 300%、アニールを行う場合 700%20 秒間という条件を最適とした。

表 4.1 からスパッタ法で成膜した ITO の方がスプレー法で成膜したものよりも低い抵抗値を示した。しかし、スプレー法で成膜した ITO は 10<sup>-4</sup> 台後半という今回実験で得られた膜より低い抵抗率を得ている報告がある。同じ条件下で作製しているはずであるので、ホットプレートの種類による基板への熱の伝わり易さの影響など引き続き検討が必要である。

### 4.1.2 ITO 薄膜の光学特性

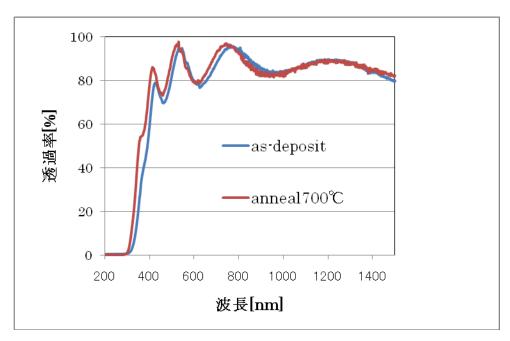

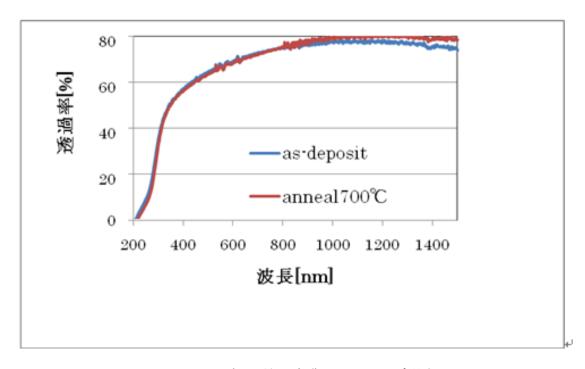

図 4.4 にスパッタ法で成膜した時の ITO の透過率について示す。試料は as-deposit 状態と アニールを 700 でで 20 秒間行ったものである。

図 4.4 スパッタ法 ITO 透過率のアニール効果

図 4.5 にスプレー法で成膜した時の ITO の透過率について示す。試料は as-deposit 状態と アニールを 700  $^{\circ}$  で 20 秒間行ったものである。

図 4.5 スプレー法で成膜した ITO の透過率

図 4.4 よりスパッタ法で ITO を成膜した時、as-deposit でもアニール後でも波長 800nm で可視光での透過率が 80%以上の値を示した。

図 4.5 よりスプレー法で ITO を成膜した時、as-deposit でもアニール後でも波長 800nm で可視光での透過率が 80%以上の値を示した。

図 4.4 と図 4.5 による、成膜方法の違いにより、どちらも ITO の透過率は高く、波形が異なることがわかる。これは、分光光度計の光の反射によるもので、スパッタ法で成膜した時の方がスプレー法で成膜した時よりも膜が均一であるためと考えられる。

# **4.2** スプレー法とスパッタ法による **ITO**/**GaAs** の **I**-**V** 特性及びコンタクト抵抗の比較

ここでは、p·GaAs、n·GaAs 基板上に、ITO をスパッタ法とスプレー法それぞれの成膜方法で堆積し、I-V 特性とコンタクト抵抗率の比較を行った。

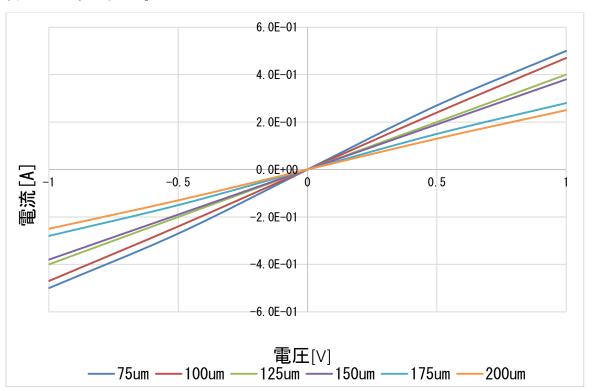

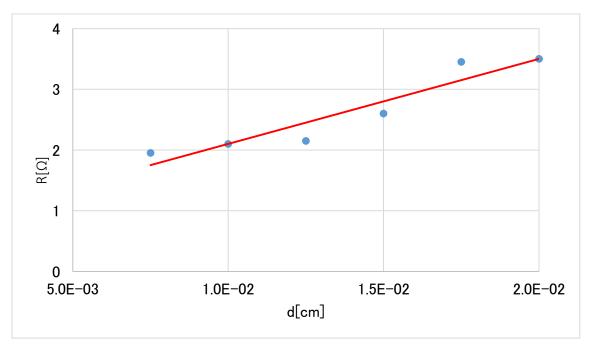

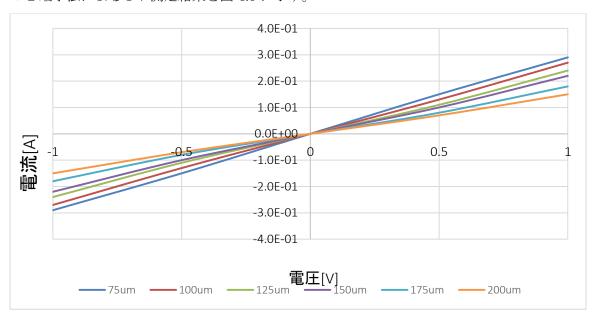

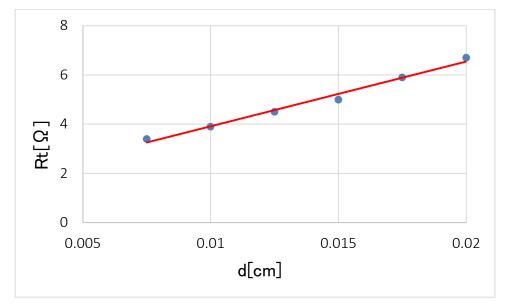

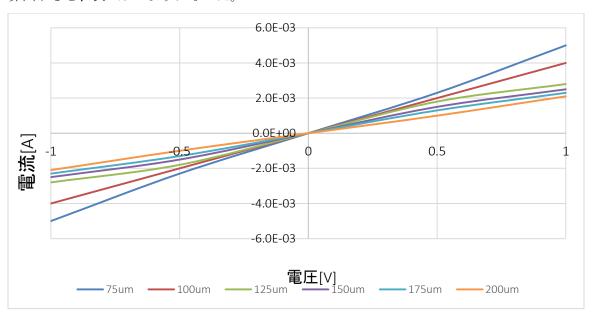

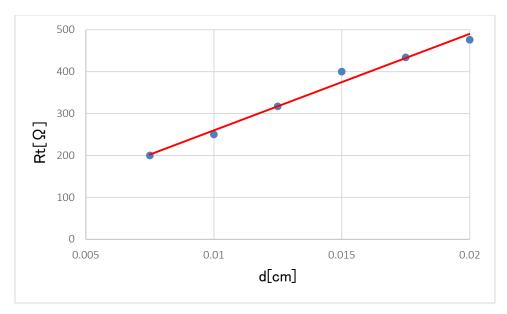

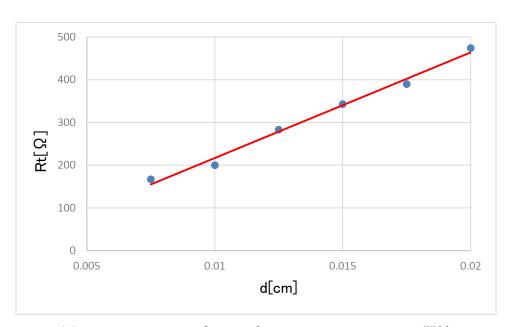

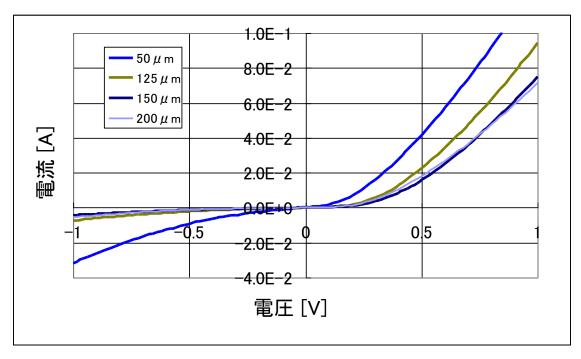

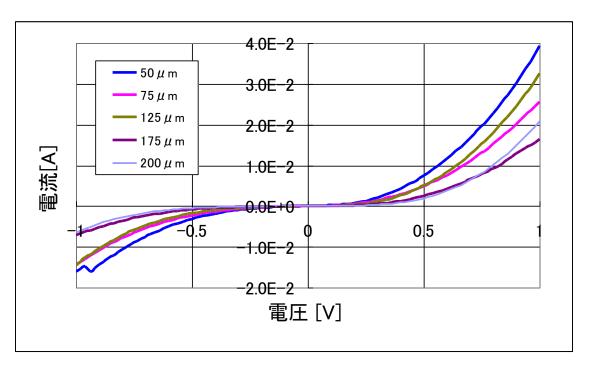

スプレー法で ITO を p-GaAs 基板上に成膜し、as-deposit 時の 2 端子法による I-V 測定結果を図 4.6 に示す。得られた I-V 特性から、CTLM パターンの円環のギャップ幅に対応する抵抗値をプロットすると図 4.7 のようになった。図 4.7 より、固有接触抵抗率を算出すると、表 4.2 のようになった。

図 4.6 as-deposit 時:スプレーITO/p-GaAsの I-V 特性

図 4.7 as-deposit 時:スプレーITO /p-GaAs の Rt-d 関係

表 4.2 as-deposit : スプレーITO/ p-GaAs の固有接触抵抗率 (Rc : 接触抵抗、Lt : 伝搬長、 $\rho_{\rm c}$  : 接触抵抗率)

| Rc [Ω]                                            | 5.46E+00 |

|---------------------------------------------------|----------|

| Lt [cm]                                           | 7.73E-03 |

| $ ho_{ m c} \left[ \Omega \cdot { m cm}^2  ight]$ | 3.26E-04 |

次に、スパッタ法で ITO を p-GaAs 基板上に成膜し、アニールを行わなかった時の 2 端子法による I-V 測定結果を図 4.8 に示す。I-V 特性が線形でないと、固有接触抵抗率の算出が行えないため、図 4.8 の Rt-d グラフは計算していない。

図 4.8 as-deposit 時:スパッタ ITO/ p-GaAs の I-V 特性

スプレー法で ITO を p-GaAs 基板上に成膜し、 $700^{\circ}$ Cで 20 秒間のアニールを行なった時の 2 端子法による I-V 測定結果を図 4.9 に示す。

図 4.9 700℃アニール: スプレーITO /p-GaAs の I-V 特性

得られた I-V 特性から、CTLM パターンの円環のギャップ幅に対応する抵抗値をプロット すると図の 4.10 のようになった。図 4.10 より、固有接触抵抗率を算出すると、表 4.3 のよ

#### うになった。

図 4.10 700℃アニール: スプレーITO/p-GaAs の Rt-d 関係

表 4.3 700℃アニール:スプレーITO /p-GaAs の固有接触抵抗率

| Rc [Ω]                                          | 1.16E+01 |

|-------------------------------------------------|----------|

| Lt [cm]                                         | 4.09E-03 |

| $ ho_{ m c} \left[\Omega \cdot { m cm}^2 ight]$ | 1.94E-04 |

スパッタ法で ITO を p-GaAs 基板上に成膜し、 $700^{\circ}$ Cで 20 秒間アニールを行なった時の 2 端子法による I-V 測定結果を図 4.11 に示す。得られた I-V 特性から、CTLM パターンの円環のギャップ幅に対応する抵抗値をプロットすると図 4.12 のようになった。図 4.12 より、固有接触抵抗を算出すると、表 4.4 のようになった。

図 4.11 700℃アニール: スパッタ ITO/ p-GaAs の I-V 特性

図 4.12 700℃アニール:スパッタ ITO/ p-GaAs の Rt-d 関係

表 4.4 700°Cアニール: スパッタ ITO/ p-GaAs の固有接触抵抗

| Rc [Ω]                                | 1.00E+1 |

|---------------------------------------|---------|

| Lt [cm]                               | 4.97E-3 |

| $ ho c \left[\Omega \cdot cm^2 ight]$ | 2.47E-4 |

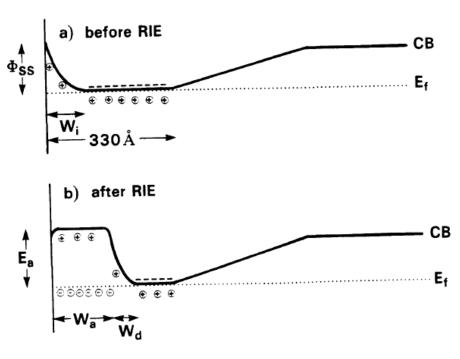

p-GaAs 基板では、スプレー法で成膜した場合、as-deposit 状態の時、オーミック特性となり、固有接触抵抗率  $3.26 \times 10^4 [\Omega \cdot \text{cm}^2]$  を得た。 $700^\circ \text{C}$ で 20 秒間アニールした時、オーミック特性となり、固有接触抵抗率  $1.94 \times 10^4 [\Omega \cdot \text{cm}^2]$  を得た。一方、スパッタ法で成膜した場合、as-deposit 状態で、非オーミック特性を得た。 $700^\circ \text{C}$ で 20 秒間アニールした時、オーミック特性となり、固有接触抵抗率  $2.47 \times 10^4 [\Omega \cdot \text{cm}^2]$  を得た。それの原因に関しては、図 4.13 に表すように、プラズマによる高いエネルギーの粒子を基板に衝突させるので、基板へのダメージの発生することにより、禁止帯にアクセプタ準位を差し入れ、電子トラップという欠陥が生じ、電子がアクセプタに捕まって、イオン化になって、ドーピング濃度が減り、空乏層の幅が広かり、トンネリング効果がなくなるため、オーミック特性にならないと考えられる。また、p-GaAs の基板では、アニールをすると、この欠陥がきえてしまい、オーミック特性になる

図 4.13 スパッタ前後のバンド図

p・GaAs 基板上に ITO をスプレー法で成膜した場合とスパッタ法で成膜した場合とを比較すると、スプレー法では as・deposit 状態でオーミック特性を得られたことに意義がある。アニールを行わずにオーミック特性を得られたということは、試料作製の工程が簡素化するだけでなく、熱による試料へのダメージも抑えられる。また、アニールした時の固有接触抵抗率の値を比較すると、スプレー法で  $1.94\times10^4[\Omega\cdot cm^2]$ 、スパッタ法で  $2.47\times10^4[\Omega\cdot cm^2]$ とほぼ同等の値を得ることができた。成膜時における、スパッタのプラズマによる GaAs 基板へのダメージを考慮すれば、基板へのダメージのないスプレー法で成膜した試料で同等の固有接触抵抗率が得られたので、スパッタ法よりもスプレー法で ITO を成膜した方が良いと言える。

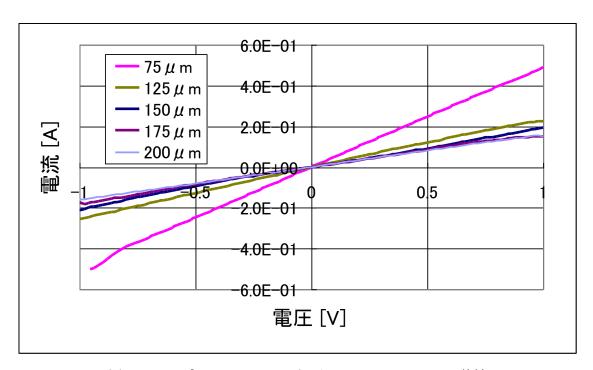

次に、スプレー法で ITO を n-GaAs 基板上に成膜し、as-deposit 時の 2 端子法による I-V 測定結果を図 4.14 に示す。得られた I-V 特性から、CTLM パターンの円環のギャップ幅に対応する抵抗値をプロットすると図 4.15 のようになった。図 4.15 より、固有接触抵抗率を算出すると、表 4.5 のようになった。

図 4.14 as-deposit: スプレーITO/n-GaAs の I-V 特性

図 4.15 as-deposit:スプレーITO/n-GaAs の Rt-d 関係

表 4.5 as-deposit: スプレーITO/n-GaAs の固有接触抵抗

| Rc [Ω]                              | 1.05E+03 |

|-------------------------------------|----------|

| Lt [cm]                             | 1.28E-03 |

| ρ <sub>c</sub> [Ω·cm <sup>2</sup> ] | 1.73E-03 |

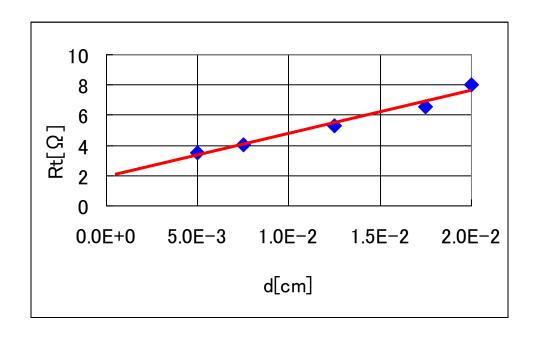

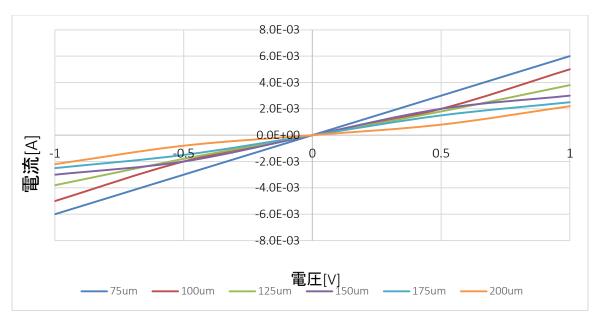

スプレー法で ITO を n-GaAs 基板上に成膜し、 $700^{\circ}$ Cで 20 秒間アニールを行なった時の 2 端子法による I-V 測定結果を図 4.16 に示す。得られた I-V 特性から、CTLM パターンの円環のギャップ幅に対応する抵抗値をプロットすると図 4.17 のようになった。図 4.17 より、固有接触抵抗を算出すると、表 4.6 のようになった。

図 4.16 700℃アニール: スプレーITO/ n-GaAs の I-V 特性

図 4.17 アニール 700℃: スプレーITO /n-GaAs の Rt-d 関係

表 4.6 アニール 700°C: スプレーITO/ n-GaAs

| $\operatorname{Rc}\left[\Omega\right]$          | 1.03E+03 |

|-------------------------------------------------|----------|

| Lt [cm]                                         | 1.24E-03 |

| $ ho_{ m c} \left[ \Omega \cdot  m cm^2  ight]$ | 1.59E-03 |

次に、スパッタ法で ITO を n-GaAs 基板上に成膜し、as-deposit 時の 2 端子法による I-V 測定結果を図 4.18 に示す。

図 4.18 as-deposit:スパッタ ITO/ n-GaAs の I-V 特性

スパッタ法で ITO を n-GaAs 基板上に成膜し、アニールを行った時の 2 端子法による I-V 測定結果を図 4.19 に示す。

n-GaAs 基板上に、ITO をスプレー法で成膜した場合とスパッタ法で成膜した場合とを比較すると、スプレー法で as-deposit 状態の時、オーミック特性となり、固有接触抵抗  $1.73\times10^{-3}[\Omega\cdot cm^2]$  を得た。700Cで 20 秒間のアニールを行った時、オーミック特性となり、固有接触抵抗率  $1.59\times10^{-3}[\Omega\cdot cm^2]$ を得た。一方、スパッタ法で成膜した場合、as-deposit と 700Cで 20 秒間のアニールを行った時、どちらでも非オーミック特性となった。

これは、スパッタ法で成膜した場合、n-GaAs 基板の表面にプラズマによる衝突をされ、欠陥が生じ、伝導帯の電子は欠陥に捕まり、キャリア密度が減少であるため、ショットキー障壁が厚く、電流がトンネルするまでに至らなかったためである。これより、n-GaAs 基板では ITO との接触界面において、成膜方法によるダメージや酸化膜の影響よりもショットキー障壁の影響の方が大きいと言える。

図 4.19 アニール 700℃時: スパッタ ITO /n-GaAs の I-V 特性

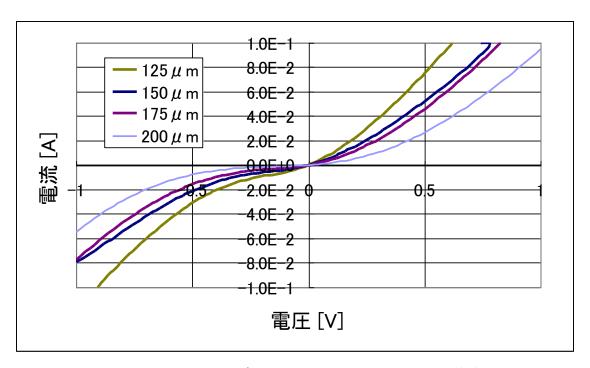

# 4.3 スプレー法による ITO/LED の立ち上がり電圧 $V_F$

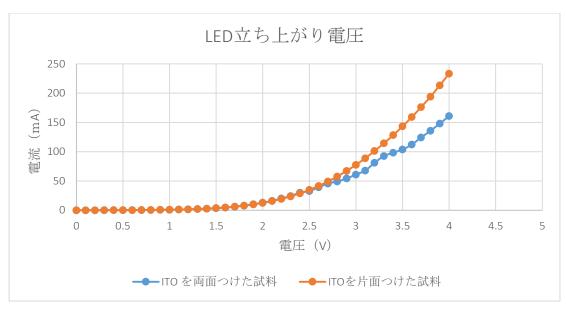

ここでは、LED 基板上に、ITO をスプレー法で片面と両面を堆積し、立ち上がり電圧  $V_F$  の比較を行った。

スプレー法で ITO を LED 基板上片面に成膜し、2 端子法による立ち上がり電圧  $V_F$  を図 4.20 に示す。

図 4.20 ITO をスプレー法でつけた LED の立ち上がり電圧  $V_F$

LED 基板上の片面に ITO をスプレー法で成膜した場合と両面に成膜した場合とを比較すると、2.7V 以下の低電圧の時はほぼ一致しているが、高電圧になると、ITO を両面につけた試料の電流が片面の場より小さくなる。例えば、電圧が 4v の時、両面に ITO をつけた試料の電流は 150mA と片面に ITO をつけた試料より 100mA 程度低くなっている。しかし、裏面で光が反射されることを考慮すると光が両面に ITO をつけた試料の方の LED として光強度が強くなることも期待される。今後では、実際に両面に ITO をつけた試料で発光効率を調べないといけないと考えておる。

## 5章 結論

本研究では新たに、成膜時の基板へダメージが懸念されるスパッタ法ではなく、スプレー法による ITO を GaAs 基板上に成膜し、成膜方法の違いによる ITO/GaAs 間の I-V 特性及び固有接触抵抗へ与える影響について調べた。スプレー法で成膜した ITO を、p-GaAs 及び n-GaAs 基板上に堆積し、ITO/GaAs の I-V 特性及びコンタクト抵抗について調べ、スパッタ法で ITO を成膜した場合と比較した。また、LED に実現できるように、立ち上がり電圧  $V_F$  を測定し、比較した。

p·GaAs 基板では、スプレー法で成膜した場合、as-deposit 状態の時、オーミック特性となり、固有接触抵抗率  $3.26 \times 10^{-4} [\Omega \cdot \text{cm}^2]$  を得た。700 Cで 20 秒間アニールした時、オーミック特性となり、固有接触抵抗率  $1.94 \times 10^{-4} [\Omega \cdot \text{cm}^2]$  を得た。一方、スパッタ法で成膜した場合、as-deposit 状態で、非オーミック特性を得た。700 Cで 20 秒間アニールした時、オーミック特性となり、固有接触抵抗率  $2.47 \times 10^{-4} [\Omega \cdot \text{cm}^2]$  を得た。p·GaAs 基板上に ITO をスプレー法で成膜した場合とスパッタ法で成膜した場合とを比較すると、スプレー法では as-deposit 状態でオーミック特性を得られたことに意義がある。アニールを行わずにオーミック特性を得られたということは、試料作製の工程が簡素化するだけでなく、熱による試料へのダメージも抑えられる。また、アニールした時の固有接触抵抗の値を比較すると、スプレー法で  $1.94 \times 10^{-4} [\Omega \cdot \text{cm}^2]$ 、スパッタ法で  $2.47 \times 10^{-4} [\Omega \cdot \text{cm}^2]$ とほぼ同等の値を得ることができた。成膜時における、スパッタのプラズマによる GaAs 基板へのダメージを考慮すれば、基板へのダメージのないスプレー法で成膜した試料で同等の固有接触抵抗が得られたので、スパッタ法よりもスプレー法で ITO を成膜した方が良いと言える。

n-GaAs 基板上に、ITO をスプレー法で成膜した場合とスパッタ法で成膜した場合とを比較すると、スプレー法で as-deposit 状態の時、オーミック特性となり、固有接触抵抗  $1.73\times10^{-3}[\Omega\cdot cm^2]$  を得た。 $700^{\circ}$ Cで 20 秒間のアニールを行った時、オーミック特性となり、固有接触抵抗率  $1.59\times10^{-3}[\Omega\cdot cm^2]$ を得た。一方、スパッタ法で成膜した場合、as-deposit と  $700^{\circ}$ Cで 20 秒間のアニールを行った時、どちらでも非オーミック特性となった。

これは、スパッタ法で成膜した場合、n-GaAs 基板の表面にプラズマによる衝突をされ、欠陥が生じ、伝導帯の電子は欠陥に捕まり、キャリア密度が減少であるため、ショットキー障壁が厚く、電流がトンネルするまでに至らなかったためである。これより、n-GaAs 基板では ITO との接触界面において、成膜方法によるダメージや酸化膜の影響よりもショットキー障壁の影響の方が大きいと言える。

また、立ち上がり電圧  $V_F$  については、LED 基板上の片面に ITO をスプレー法で成膜した場合と両面に成膜した場合とを比較すると、2.7V 以下の低電圧の時はほぼ一致しているが、高電圧になると、ITO を両面につけた試料の電流が片面の場より小さくなる。しかし、裏面で光が反射されることを考慮すると光が両面に ITO をつけた試料の方の LED として光強度が強くなることも期待される。

## 謝辞

本研究を進めるにあたり、研究内容に関する助言を頂き、また的確に指導して下さった野崎眞次教授、内田和男准教授、SVBLの加藤さん心より感謝致します。

指導教官の野崎眞次教授には研究の方針や課題を考えていただき、ご指導頂きました。副 指導教官の内田和男准教授には研究の方針等で的確なアドバイスを賜りました。加藤さんに は、実験装置の修理や装置の使い方の指導等でお世話になりました。

最後に、博士の張東元さん、同期の長谷川源君、青木遼太郎君、THAN HONG PHUCさん、 浅野圭太君、五十嵐慎君、中村元彦君、ROFFI 君、本当にありがとうございます。誰一人欠けても この二年間はありませんでした。また、M1 と学部 4 年生にも研究室生活を送っていく上で様々 なことに協力して頂いたり、研究に関してアドバイスを頂いたりしました。感謝いたします。 今後の研究室等での生活を楽しく過ごし、研究など、頑張ってください。2 年間同じ部屋で 過ごした修士 2 年の皆様、日々の研究生活でお世話になり、ありがとうございました。

皆様のおかげでこの論文を完成させることが出来ました。貴重な体験となる研究室生活を 送ることができたことを改めて御礼申し上げます。では。

> 2013年1月 ハオ ウェン ダより

# 参考文献

- [1] C.Guillen, J.Herrero: Journal of Applied Physics 1010 073514 (2007)

- [2]T.Ban, Y.Ohya, Y.Takahashi: Journal of Applied Physics 83 No.5 (1998) 2631-2645

- [3]G.Frank, H.Kostlin : Applied Physics A 27 (1982) 197-206

- [4]K.Utsumi, H.Iigusa: Tosoh Research & Technology Review Vol.47 (2003)

- [5]日本学術振興会 透明酸化物光・電子材料第 166 委員会編, 透明導電膜の技術 (1999)

- [6]S.Takazawa, S.Ukishima, N.Tani, S.Ishibashi: ULVAC Technical Journal No.64 2006

- [7]Y.Sawada, C.Kobayashi, S.Seki, and H.Funakubo: Thin Solid Films 409 (2002) 46-50

- [8]S.Seki,M.Wakana,Y.Kasahara,Y.Seki,T.Kondo,M.Wang, T.Uchida, K.Haga, Y.Sawada

- : Japanese Journal of Applied Physics Vol.46 No.10A (2007) 6837-6841

- [9]T.kondo, H,Funakubo, K.Akiyama, H.Enta, Y.Seki, M.H.Wang, T.Uchida, Y.Sawada Journal of Crystal Growth 311 (2009) 642-646

- [10]T.Kondo, Y.Sawada, K.Akiyama, H.Funakubo, T.Kiguchi, S.Seki, M.H.Wang, T.Uchida: Thin Solid Films 516 (2008) 5864-5867

- [11]D.Peredins, L.Gauckler: Journal of Electronics 14 (2005) 103-111

- [12] T. Fukano, T. Motohiro: Solar Energy Materials & Solar Cells 82 (2004) 567-575

- [13]T.Kawashima, T. Ezure, K.Okada, H.Matsui, K.Goto, N.Tanabe

- :Journal of Photochemistry and Photobiology A Chemistry 164 (2004) 199-202

- [14]T.Kawashima, H.Matsui, N.Tanabe: Thin Solid Films 445 (2003) 241-244

- [15]I.A.Rauf J.Appl.Phys. Vol79, No.8, 15 (1996) 4057-4065

- [16] W.Jiang, M.wu, H.Yu, C.Huang, C.Sung, J.Chi: Solid-State Electronics 46 (2002) 1945-1948

- [17]H.C.Wang, Y.K.Su, C.L.Lin, W.B.Chen, S.M.Chen: IEEE Photonics Technology Letters Vol.14 No.11 (2002) 1491-1493

- [18]J.Rechid, K.Heime: Solid-State Electronics 44 (2000) 451-455

- [19]Y.H.Aliyu, D.V.Morgan, R.W.Bunce: Electronics Letters Vol. 28 No. 2 (1992) 142-144

- [20] A. Salehi, K.N. Toosi: Electronics Letters Vol. 34 No. 1 (1998) 129-131

- [21]R.Horng, Y.Lien, W.Peng, D.Wuu, C.Tseng, C.Seieh, M.Huang, S.Tsai, J.Liu: Jpn.J.Appl.Phys. Vol.40 (2001) 2747-2751

- [22] 甲斐敬紹, 卒業論文 (電気通信大学電気通信学部電子工学科) (2004)

- [23] 山本篤, 卒業論文(電気通信大学電気通信学部電子工学科) (2008)

- [24] 木村仁志. 修士論文(雷気通信大学電気通信学研究科電子工学専攻)(2008)

[25] 荒井優,修士論文(電気通信大学電気通信学研究科電子工学専攻) (2009)

# 付録

# 付録 A 四探針法

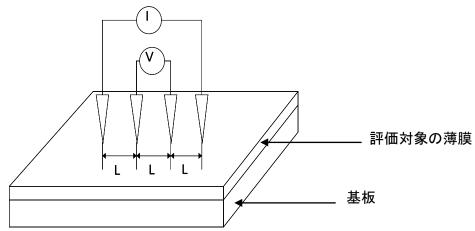

本研究で作成した薄膜の抵抗率測定は、図に示すような四探針法で行った。この方法は薄膜の抵抗率測定には便利な方法である。4 本の探針を一直線上に等間隔(L)に並べ一定加重で圧着し、外側の2探針間に電流Iを流し、内側の2探針間の電圧Vを測定するものである。

図 A.1 4 探針法による測定

尚、電流源の出力インピーダンス、電圧計の入力インピーダンスはともに十分に大きいものとする。電流値 I、電圧値 V を用いて抵抗率  $\rho$  は式 A.1 によって得られる。

$$\rho = \frac{2\pi LV}{I}$$

(A.1)

ただし、この式が成立するのは、試料の膜厚が探針の間隔に比べて十分に大きい場合であり、薄膜などの試料では補正が必要である。すなわち、探針間隔 L が試料の膜厚 d に比べ十分に大きい場合、さらに試料の大きさに比べて膜厚が十分小さい場合、補正係数  $CF = \pi / \ln 2$  = 4.54 と膜厚 d から式 A.2 により計算できる。

$$\rho = \frac{\mathbf{V}}{\mathbf{I}} \cdot d \cdot \mathbf{CF} \tag{A.2}$$

# 付録B 電子ビーム蒸着

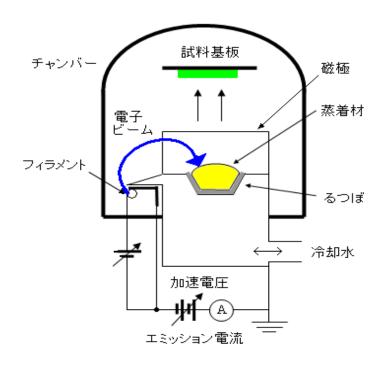

電子ビーム蒸着とは、図 B.1 に示すような回路を用いて、蒸発材料に電子線を照射し、加熱蒸着させる方法である。原理的には、加速電圧を約  $2\sim3[kV]$ 程度かけることによって加熱されたフィラメントから電子ビームによる電流が供給され、電界によって加速された電子が磁界で曲げられ蒸着材に衝突し、加熱され蒸発する。

図 B.1 電子ビーム蒸着法

電子線の収束により、局所的な高温が得られる。また、銅製るつぼを充分冷却することによって高温を得ることが可能になり、Pt(プラチナ)、Ni(ニッケル)、Mo(モリブデン)、W(タングステン)などの高融点金属などの材料の薄膜形成も可能となる。また、抵抗加熱蒸着法と比較してボートなどの蒸着源との反応が少ないために不純物の混入が少なく、高純度の薄膜形成が可能である。さらに蒸発源の寿命が非常に長い、蒸発速度が大きい、熱応答性がよいので性格に蒸発速度を制御できる、合金や化合物を容易に蒸発できる、取り扱いが容易などの特長がある。しかし、コストが高いという欠点もある。

# 付録 C RF マグネトロンスパッタリング法

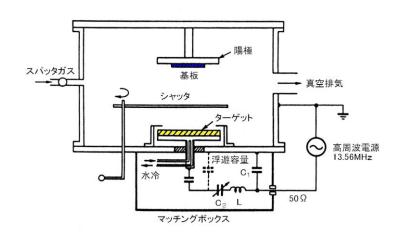

代表的な RF スパッタリング装置の概略図を図に示す。

図 C.1 RF スパッタリング装置概略図

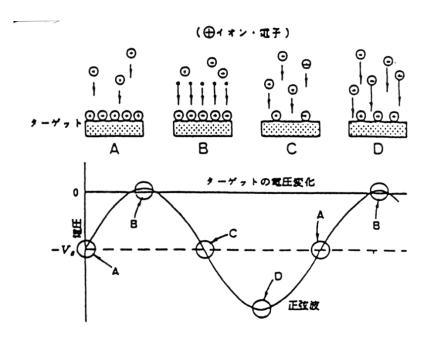

一対の陰極と陽極からなる 2 極冷陰極グロー放電管構造で、陰極はターゲットに相当し、陽極は基板ホルダーの役目を兼ねる。チャンバー内の真空度を 10-3Pa 程度に保ち、Ar 等の不活性ガスを導入する。電極間に電圧を印加するとグロー放電が発生し、放電空間にはAr プラズマが形成される。Ar 正イオンは電界で加速され運動エネルギーを得て陰極に衝突する。ここでターゲットイオンと運動量交換をし、ターゲット材料を弾き飛ばすと同時に二次電子を発生させ、ターゲット表面をスパッタ蒸着させる。スパッタ粒子は、陽極上に配置された基板上に堆積され、ターゲット材料からなる薄膜が形成される。

スパッタリング法には直流・交流の2種類があるが、直流で ITO や InTiO 等の絶縁物をスパッタしようとしても、正イオンがターゲットに衝突するたびにターゲット表面が正電位に帯電していく。そのため陽極とターゲット表面との電位差がなくなってしまうためスパッタ放電は持続しない。一方直流スパッタリング装置の直流電源を交流電源に代えると絶縁物ターゲットの表面に正イオンと電子が両方とも衝突するためターゲット表面における正電位の帯電は見られない。このため高周波電源を用いると絶縁物のターゲットにおいてもグロー放電が持続する。このときプラズマ放電中の電子はイオンよりも移動度が大きいためターゲット表面に電子が過剰に蓄積し、ターゲット表面は負電位にバイアスされつづけるために、絶縁物のターゲットでもスパッタされる。また DC スパッタリング法と比較してプラズマ発生時の Ar 圧力が低く設定できるため比較的プラズマ放電が安定している。

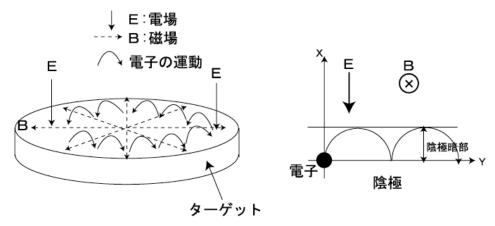

図 C.2 陰極のバイアス印加モデル

更に、ターゲット面に平行な磁界を発生させ、捕獲した 2 次電子を利用してイオン化を促進し、堆積速度を上げるスパッタ法をマグネトロンスパッタと言う。円盤状のターゲットの裏面に磁石を装着した構造では、磁力線が N から S へ 終端する途中で必ずターゲット表面に平行な漏洩磁界成分がある。陰極表面から叩き出された二次電子は、ローレンツ力によって  $E \times B$  方向にドリフト運動し、電場と磁場の直交する方向にサイクロイド曲線を描く。さらにそのドリフト運動が、1 つの無終端の軌跡を形成することによって放電が維持されることを特徴とする。図に平板マグネトロン型ターゲット電極及びターゲット上での電子の運動を示す。

電子のドリフト運動と閉じた軌跡の2つの点から陰極近傍で電離衝突頻度が極めて高くなり、比較的低い印加電圧と低い圧力でも放電を維持し、大電流密度放電が可能になり、スパッタリング速度を著しく大きくすることができる。

図 C.3 平板マグネトロン型ターゲット電極及びターゲット上での電子の運動

このようにマグネトロンスパッタ法は生産性の高いスパッタリング法である。しかし、電子を拘束するのに必要なターゲット表面に平行な磁力線は漏洩磁力線のごく一部で、 ターゲット面から垂直に出している中心部と周辺部は侵食され、電子の軌跡を中心にターゲットを激しくエッチングするため、短時間のうちにエロージョンと呼ばれる侵食領域が現れ、ターゲット表面は平面でなく不均一な凹凸状態となる。結果として、ターゲットの利用効率は20%~30%程度になってしまう。

# 付録**D** CTLM 法を用いた I-V 特性、及びコンタクト 抵抗の測定

オーミックコンタクトの性能指数は接触抵抗率  $\rho c$ (単位 :  $\Omega cm2$ )で表され、式 D.1 で表される。

$$\rho_C \equiv \left(\frac{\partial V}{\partial I}\right)_{V=0} \tag{D.1}$$

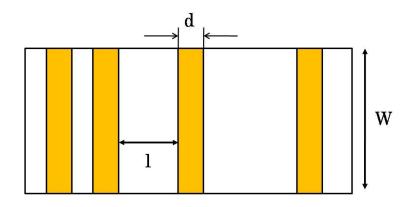

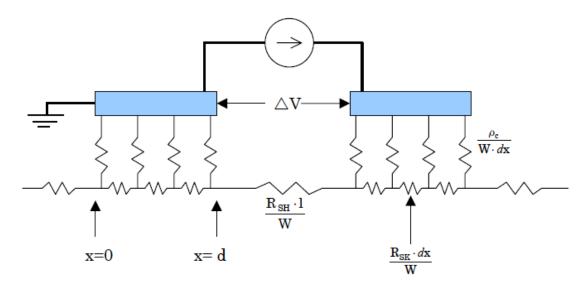

この接触抵抗率の測定には(Transmission Line Model: TLM)法が用いられる。TLM とは、図 D.1 のように電極とその真下の半導体層を伝送回路と等価と考えて解析する方法であり、その電極の形状には以下に示すように長方形又は円形のものが一般的に用いられている。

## D.1 TLM 法

TLM 測定は、図 E-1 に示すような長方形のコンタクトを用いて測定を行なう。二つのコンタクトパッド間で計測される全抵抗 R は接触抵抗  $R_{\rm C}$  の 2 倍+半導体層の抵抗  $R_{\rm S}$  なので、

図 D.1 TLM 測定パターン

$$R = 2R_C + R_S \tag{D.2}$$

$$R_C = \frac{R_{SK} \cdot L_t}{W} \tag{D.3}$$

$$R_S = \frac{R_{SH} \cdot l}{W} \tag{D.4}$$

ここで、 $R_{SH}$ : コンタクト直下以外のシート抵抗(パッド間のシート抵抗)[ $\Omega$ ]、 $R_{SK}$ : コンタクト直下のシート抵抗[ $\Omega$ ]、Lt: 伝搬長[cm]、W: コンタクトパッド幅[cm]、1: パッド間の間隔[cm]である。

パッド間の抵抗を数点測定し、パッド間の全抵抗 R とパッド間距離 1 との直線関係が 求まれば、傾きから  $R_{SH}/W$  が求まり、R 軸の切片がそれぞれ  $2R_{C}$ 、1 軸の切片が-2L t であるので、この方法を用いて接触抵抗  $R_{C}$  を求めることができる。ここで、 $R_{SH}=R_{SK}$  と仮定し、d >>Lt で電圧降下が電極の端の部分のみで起こると仮定すると、接触抵抗は電流の流れる部分の面積( $Lt\cdot W$ )と接触抵抗の積で表すことができるので、

$$\rho_C = R_C \cdot L_t \cdot W = \frac{R_{SK} \cdot L_t}{W} \cdot L_t \cdot W = R_{SK} \cdot L_t^2$$

(D.5)

で与えられる。

図 D.2 長方形電極を並べたときの伝送回路の様子

## D.2 CTLM 法

図 D,1 のように長方形を並べて接触抵抗の測定を行う方法では、コンタクトエッジでの電流が測定結果に影響するので、この電流を除去するために、電極と接触しない領域をエッチングしてメサ構造にする必要がある。そのため、このパターンはメサエッチングを含むプロセスによって製作しなければならず、手順が複雑である。この複雑さを避けるためにパターンをリング状にした TLM 測定法が Circular-TLM: CTLM 法である。

図 D.3 CTLM 測定パターン

CTLM 測定に用いるリング状のパターンを図 D.3 に示す。この CTLM 測定を用いると、電極間の全抵抗 R は次式で与えられる。

$$R = \frac{R_{SH}}{2\pi} \left[ L_t \left( \frac{1}{a_2} + \frac{1}{a_1} \right) + \ln \left( \frac{a_2}{a_1} \right) \right]$$

(D.6)

ここで、 $R_{SH}$ : コンタクト直下以外のシート抵抗[ $\Omega$ ]、a1: リング内径[cm]、

a2: リング外形[cm]、Lt: 伝搬長[cm]である。

d=a2-a1とおくと、ギャップの面積は

$$S = \pi (a_2^2 - a_1^2) = \pi (a_2 + a_1)(a_2 - a_1)$$

=  $\pi (a_2 + a_1)d$  (D.7)

となる。よって(a2+a1)が同じパターンであると面積は d に比例する。つまり、Rt-d 特性グラフは線形近似でき、その時の d 軸切片が-2Lt となる。これより伝搬長 Lt が求まる。また、a2、a1>> d であるとし、式(D.6)の第 2 項についてマクローリン展開を行なうと、

$$f\left(\frac{d}{a_2}\right) = \ln\left(\frac{a_2}{a_1}\right) = \ln\left(\frac{a_2}{a_2 - d}\right) = -\ln\left(1 - \frac{d}{a_2}\right)$$

$$= f(0) + f'(0) \cdot \frac{d}{a_2} + \cdots$$

$$\approx \frac{d}{a_2 - d}$$

$$\approx \frac{d}{a_2} \quad (\because a_2 >> d)$$

(D.7)

従って、最終的に式(E.6)は、

$$R \approx \frac{R_{SH}}{2\pi a_2} \left( d + 2L_t \right) \tag{D.8}$$

となる。これより d と R の関係が求まれば、傾きから R。を求めることができる。また、R 軸の切片から Lt を求まるため、電極の接触抵抗  $\rho_C$  は次式により計算できる。

$$L_{t} = \sqrt{\frac{\rho_{c}}{Rc}}$$

$$\rho_{c} = L_{t}^{2} \cdot R_{c}$$

(D.9)

本研究では、ヒューレットパッカード社製の半導体パラメータアナライザ HP4155A を用いて、電極パッド間の I-V 特性(傾き:抵抗値)を測定した。また、測定用探針は金探針を用いた。