# Rapid Single-Flux-Quantum NOR Logic Gate Realized through the Use of Toggle Storage Loop

| 著者(英)             | Yoshinao MIZUGAKI, Koki YAMAZAKI, Hiroshi |

|-------------------|-------------------------------------------|

|                   | SHIMADA                                   |

| journal or        | IEICE Transactions on Electronics         |

| publication title |                                           |

| volume            | E103.C                                    |

| number            | 10                                        |

| page range        | 547-549                                   |

| year              | 2020-10-01                                |

| URL               | http://id.nii.ac.jp/1438/00009627/        |

doi: 10.1587/transele.2020ECS6005

## **BRIEF PAPER**

# Rapid Single-Flux-Quantum NOR Logic Gate Realized through the Use of Toggle Storage Loop

Yoshinao MIZUGAKI<sup>†a)</sup>, Member, Koki YAMAZAKI<sup>†</sup>, and Hiroshi SHIMADA<sup>†</sup>, Nonmembers

**SUMMARY** Recently, we demonstrated a rapid-single-flux-quantum NOT gate comprising a toggle storage loop. In this paper, we present our design and operation of a NOR gate that is a straightforward extension of the NOT gate by attaching a confluence buffer. Parameter margins wider than  $\pm 28\%$  were confirmed in simulation. Functional tests using Nb integrated circuits demonstrated correct NOR operation with a bias margin of  $\pm 21\%$

**key words:** superconducting digital gates, Nb IC, single-flux-quantum circuits

#### 1. Introduction

Superconducting digital circuits have been expansively developed for the last three decades [1]–[11]. Among several superconducting digital technologies, the rapid single-flux-quantum (RSFQ) technology [1], where the existence and absence of a single flux quantum (SFQ) in a superconducting loop respectively represent the binary digital states of "1" and "0", is the most developed and widely used. One achievement is a 33 GHz-clock RAM-embedded microprocessor in which 10,603 Nb Josephson junctions (JJs) are integrated [12].

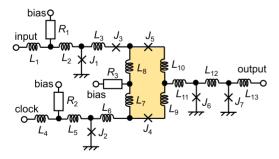

For designing RSFQ digital circuits, logic cell libraries, in which tens of logic cells are compiled, have been established and being extended. Recently, we experimentally demonstrated operation of a NOT gate [13], of which the equivalent circuit is shown in Fig. 1, as an alternative NOT

**Fig. 1** Equivalent circuit of a NOT gate comprising a toggle storage loop. All Josephson junctions (JJs) are externally shunted to make the McCumber parameter  $\beta_c$  be 0.89 for ensuring compatibility with the CONNECT library [14]. The storage loop is filled in light brown.

Manuscript received February 28, 2020.

Manuscript revised March 27, 2020.

Manuscript publicized April 13, 2020.

<sup>†</sup>The authors are with The University of Electro-Communications, Chofu-shi, 182–8585 Japan.

a) E-mail: y.mizugaki@uec.ac.jp DOI: 10.1587/transele.2020ECS6005 logic cell compatible with the library referred to as "CONNECT" [14]. Its configuration was similar to the NOT gates described in [15] and [16]. By using this NOT gate structure, we succeeded to reduce the cell size from  $80 \,\mu\text{m} \times 80 \,\mu\text{m}$  to  $80 \,\mu\text{m} \times 40 \,\mu\text{m}$  [13].

Its NOT operation sequence is briefly explained as follows. When an SFQ comes from the input terminal, it is stored in the toggle storage loop  $(J_4-L_7-L_8-J_5-L_{10}-L_9)$  through  $J_1$  and  $J_5$ . Then, an SFQ from the clock terminal is transferred not to the output terminal but to the storage loop through  $J_4$ , which annihilates the stored SFQ. It means that the input "1" results in the output "0". When an SFQ comes from the clock terminal without a preceding SFQ from the input terminal, it is transferred to the output terminal. This means that the input "0" results in the output "1".

This NOT gate can be applied to other negative logic gates. It was numerically presented that a NOR gate was realized by combining this NOT gate and a confluence buffer [13], [16], whereas experimental verification was not conducted. Since a NOR gate is one of the universal logic gates that can implement any Boolean function, it is worth while to verify the operation of the proposed NOR gate in experiments. In this paper, we present our design and functional tests of the NOR gate on niobium integrated circuits.

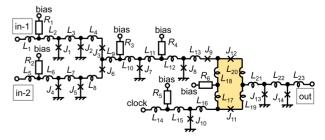

### 2. Configurations of NOR Gate

The equivalent circuit of the NOR gate is shown in Fig. 2. It consists of a confluence buffer and a NOT gate. More specifically, the input terminal of the NOT gate shown in Fig. 1 is replaced with a confluence buffer with two input terminals, which realizes a 2-input NOR function. The loop consisting of  $J_{11}$ - $L_{17}$ - $L_{18}$ - $J_{12}$ - $L_{20}$ - $L_{19}$  works as a toggle storage loop.

We obtained the circuit parameters by using a

**Fig. 2** Equivalent circuits of the NOR gate. All JJs are externally shunted to make the McCumber parameter  $\beta_c$  be 0.89 for ensuring compatibility with the CONNECT library. The storage loop is filled in light brown.

**Table 1** Optimization results of the circuit parameters for the NOR gate. Values of inductances  $(L_i)$ , junction critical currents  $(J_i)$ , and resistances  $(R_i)$  are presented in units of pH,  $\mu$ A, and  $\Omega$ , respectively. The nominal bias voltage is 2.5 mV. The inductance value of  $L_9$  was fixed to 0.01 pH during the optimization.

| $L_{1,5,14}$    | $L_{2,6}$            | $L_{3,7}$               | $L_{4,8}$               | $L_{10}$                  | $L_{11}$           | $L_{12}$              | $L_{13}$               |

|-----------------|----------------------|-------------------------|-------------------------|---------------------------|--------------------|-----------------------|------------------------|

| 0.83            | 1.90                 | 2.28                    | 1.23                    | 4.32                      | 1.66               | 1.42                  | 3.50                   |

| $L_{15}$        | $L_{16}$             | $L_{17}$                | $L_{18}$                | $L_{19}$                  | $L_{20}$           | $L_{21}$              | $L_{22}$               |

| 1.50            | 3.33                 | 8.97                    | 1.01                    | 0.63                      | 0.59               | 1.37                  | 5.50                   |

|                 |                      |                         |                         |                           |                    |                       |                        |

| $L_{23}$        | $J_{1,4}$            | $J_{2,5}$               | $J_{3,6}$               | $J_7$                     | $J_8$              | $J_9$                 | $J_{10}$               |

| L <sub>23</sub> | J <sub>1,4</sub> 200 | J <sub>2,5</sub><br>195 | J <sub>3,6</sub><br>148 | <i>J</i> <sub>7</sub> 165 | J <sub>8</sub> 261 | J <sub>9</sub><br>100 | J <sub>10</sub><br>196 |

|                 |                      |                         | . , .                   |                           |                    |                       |                        |

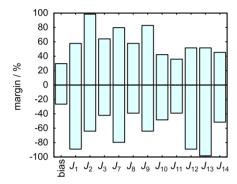

Fig. 3 Margins of the bias voltage and junction critical currents for the NOR gate.

Josephson circuit simulator "JSIM" [17] and an optimization program "SCOPE2" [18]. The obtained parameters are tabulated in Table 1 [13], whereas the margins of the bias voltage and junction critical currents are plotted in Fig. 3. Relatively satisfactory margins wider than  $\pm 28\%$  are confirmed.

We confirmed by numerical simulation that the NOR gate worked correctly at clock frequencies up to 51.3 GHz for the nominal bias voltage (2.5 mV). We also numerically simulated operation of the NOR gate cell compiled in the CONNECT library, which demonstrated that its maximum clock frequency for the nominal bias voltage was 36.8 GHz. These results indicated that the NOR gate developed in this work would have advantage for high speed operation.

Our NOR gate is a straightforward extension of the NOT gate by attaching a confluence buffer, and therefore, it would not offer the most efficient design. In addition, our NOR gate is designed to be compatible with cells in the CONNECT library. For example, Myoren *et al.* presented another RSFQ NOR gate with numerical results [19]. The number of JJs in their NOR gate was 6, whereas that in our NOR gate is 14. However, our NOR gate would provide a guide to other negative logic functions utilizing a toggle storage loop.

#### 3. Experimental Results and Discussion

We designed test circuits of the NOR gate with digital cells in the CONNECT library. Inductance extraction program

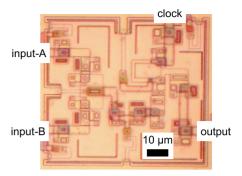

**Fig. 4** Photomicrographs of a NOR gate cell. The cell size is  $80\,\mu\mathrm{m} \times 80\,\mu\mathrm{m}$ .

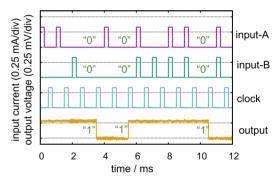

**Fig. 5** Waveforms of functional tests of a NOR gate. An SFQ was fed to the input-A, input-B, and clock terminal at the rising edges of input current signals. For the output signal of an SFQ-to-dc converter, no voltage transition represented "0" output, whereas a high-to-low or low-to-high voltage transition represented "1" output.

"InductEX" [20] was used for design of inductance layouts. Conventional Josephson transmission lines, dc-to-SFQ converters, and an SFQ-to-dc converter were used for the IO elements. Test chips were fabricated using a  $25-\mu A/\mu m^2$  Nb/AlO<sub>x</sub>/Nb integration process [21] at the National institute of Advanced Industrial Science and Technology, Japan. Figure 4 shows photomicrographs of a fabricated NOR gate cell, each of which the dimensions are  $80 \, \mu m \times 80 \, \mu m$ .

In measurements, a test chip was cooled in a liquid helium bath. The output voltage was acquired with a digital oscilloscope via a 40-dB low-noise preamplifier. Low-speed tests to confirm the gate functions were conducted.

Results for functional tests of a NOR gate are presented in Fig. 5. Correct operations were confirmed. The bias margin was  $\pm 21\%$ , slightly narrower than the numerical result of  $\pm 28\%$ .

#### 4. Conclusion

We presented our design and operation of a NOR gate comprising a confluence buffer and a toggle storage loop. The NOR gate was a straightforward extension of a NOT gate, a toggle storage loop with a confluence buffer attached. Functional tests using Nb/AlO<sub>x</sub>/Al integrated circuits demonstrated correct NOR operation. An experimental bias margin as wide as 21% was confirmed for the NOR gate. The

results of the NOR gate operation opened a path for other negative logic functions utilizing a toggle storage loop.

#### Acknowledgments

The authors thank the lab members in UEC Tokyo for their fruitful discussion and technical support. This research work was partly supported by JSPS Grant-in-Aid for Scientific Research 17K04979, and by VLSI Design and Education Center (VDEC), the University of Tokyo in collaboration with Cadence Design Systems, Inc. Test circuits used in this study were fabricated using the Nb STP2 process in the Superconducting Clean Room (CRAVITY) at the National Institute of Advanced Industrial Science and Technology (AIST). The stable supply of liquid helium from the Coordinated Center for UEC research Facilitites is also acknowledged.

#### References

- [1] K.K. Likharev and V.K. Semenov, "RSFQ logic/memory family: A new Josephson-junction technology for sub-terahertz-clock-frequency digital systems," IEEE Trans. Appl. Supercond., vol.1, no.1, pp.3–28, March 1991. DOI: 10.1109/77.80745

- [2] K. Nakajima, H. Mizusawa, H. Sugahara, and Y. Sawada, "Phase mode Josephson computer system," IEEE Trans. Appl. Supercond., vol.1, no.1, pp.29–36, March 1991. DOI: 10.1109/77.80746

- [3] M. Hosoya, W. Hioe, J. Casas, R. Kamikawai, Y. Harada, Y. Wada, H. Nakane, R. Suda, and E. Goto, "Quantum flux parametron: A single quantum flux device for Josephson supercomputer," IEEE Trans. Appl. Supercond., vol.1, no.1, pp.77–89, March 1991. DOI: 10.1109/77.84613

- [4] M. Dorojevets, P. Bunyk, and D. Zinoviev "FLUX chip: Design of a 20-GHz 16-bit ultrapipelined RSFQ processor prototype based on 1.75-\(\mu\mathrm{T}\) LTS technology," IEEE Trans. Appl. Superconduct., vol.11, no.1, pp.326–332, March 2001. DOI: 10.1109/77.919349

- [5] M. Tanaka, F. Matsuzaki, T. Kondo, N. Nakajima, Y. Yamanashi, A. Fujimaki, H. Hayakawa, N.Yoshikawa, H. Terai, and S. Yorozu, "A single-flux-quantum logic prototype microprocessor," Int. Solid-State Circuit Conf. Dig. Tech. Papers, San Francisco, USA, 298, Feb. 2004. DOI: 10.1109/ISSCC.2004.1332714

- [6] H. Hayakawa, N. Yoshikawa, S. Yorozu, and A. Fujimaki, "Superconducting digital electronics," Proc. IEEE, vol.92, no.10, pp.1549–1563, Oct. 2004. DOI: 10.1109/JPROC.2004.833658

- [7] O.A. Mukhanov, D. Gupta, A.M. Kadin, and V.K. Semenov, "Super-conductor analog-to-digital converters," Proc. IEEE, vol.92, no.10, pp.1564–1584, Oct. 2004. DOI: 10.1109/JPROC.2004.833660

- [8] K.K. Likharev, "Superconductor digital electronics," Physica C, vol.482, pp.6–18, Nov. 2012. DOI: 10.1016/j.physc.2012.05.016

- [9] A. Fujimaki, M. Tanaka, R. Kasagi, K. Takagi, M. Okada, Y. Hayakawa, K. Takata, H. Akaike, N. Yoshikawa, S. Nagasawa, K. Takagi, and N. Takagi, "Large-scale integrated circuit design based on a Nb nine-layer structure for reconfigurable data-path processors," IEICE Trans. Electron., vol.E97-C, no.3, pp.157–165, March 2014. DOI: 10.1587/transele.E97.C.157

- [10] N. Takeuchi, Y. Yamanashi, and N. Yoshikawa, "Adiabatic quantum-flux-parametron cell library adopting minimalist design," J. Appl. Phys., vol.117, no.17, 173912, May 2015. DOI: 10.1063/1.4919838

- [11] Y. Ando, R. Sato, M. Tanaka, K. Takagi, N. Takagi, and A. Fujimaki, "Design and demonstration of an 8-bit bit-serial RSFQ microprocessor: CORE e4," IEEE Trans. Appl. Supercond., vol.26, no.5, 1301205, Aug. 2016. DOI: 10.1109/TASC.2016.2565609

- [12] R. Sato, Y. Hatanaka, Y. Ando, M. Tanaka, A. Fujimaki, K. Takagi, and N. Takagi, "High-speed operation of random-access-memory-embedded microprocessor with minimal instruction set architecture based on rapid single-flux-quantum logic," IEEE Trans. Appl. Supercond., vol.27, no.4, 1300505, June 2017. DOI: 10.1109/TASC. 2016.2642049

- [13] K. Yamazaki, H. Shimada, and Y. Mizugaki, "Design and error-rate evaluation of RSFQ logic gates comprising a toggle storage loop," J. Phys.: Conf. Ser., vol.1590, 012042, July 2020. DOI: 10.1088/ 1742-6596/1590/1/012042

- [14] S. Yorozu, Y. Kameda, H. Terai, A. Fujimaki, T. Yamada, and S. Tahara, "A single flux quantum standard log cell library," Physica C, vol.378–381, pp.1471–1474, Oct. 2002. DOI: 10.1016/S0921-4534(02)01759-8

- [15] Stony Brook University New York RSFQ Cell Library http://www.physics.sunysb.edu/Physics/RSFQ/Lib/index.html

- [16] R.S. Bakolo and C.J. Fourie, "New implementation of RSFQ superconductive digital gates," SAIEE Africa Research Journal, vol.104, no.3, pp.90–96, Sept. 2013. DOI: 10.23919/SAIEE.2013.8531846

- [17] E.S. Fang and T. Van Duzer, "A Josephson integrated circuit simulator (JSIM) for superconductive electronics application," Int. Supercond. Electron. Conf. Tokyo, Japan, pp.407–410, 1989.

- [18] N. Mori, A. Akahori, T. Sato, N. Takeuchi, A. Fujimaki, and H. Hayakawa, "A new optimization procedure for single flux quantum circuits," Physica C, vol.357–360, pp.1557–1560, Aug. 2001. DOI: 10.1016/S0921-4534(01)00547-0

- [19] H. Myoren, Y. Wakimizu, and S. Takada, "Design of single-flux-quantum universal gates with a wide operating margin," Supercond. Sci. & Technol., vol.16, no.12, pp.1447–1451, Nov. 2003. DOI: 10.1088/0953-2048/16/12/028

- [20] C.J. Fourie and W.J. Perold, "Simulated inductance variations in RSFQ circuit structures," IEEE Trans. Appl. Supercond., vol.15, no.2, pp.300–303, June 2005. DOI: 10.1109/TASC.2005.849806

- [21] S. Nagasawa, Y. Hashimoto, H. Numata and S. Tahara, "A 380ps, 9.5mW Josephson 4-Kbit RAM operated at high bit yield," IEEE Trans. Appl. Supercond., vol.5, no.2, pp.2447–2452, June 1995. DOI: 10.1109/77.403086